# Digital Technical Journal

Digital Equipment Corporation

Volume 3 Number 4 Fall 1991

#### Editorial

Jane C. Blake, Editor Helen L. Patterson, Associate Editor Kathleen M. Stetson, Associate Editor Leon Descoteaux, Associate Editor

#### Circulation

Catherine M. Phillips, Administrator Sherry L. Gonzalez

#### Production

Mildred R. Rosenzweig, Production Editor Margaret L. Burdine, Typographer Peter R. Woodbury, Illustrator

#### Advisory Board

Samuel H. Fuller, Chairman Richard W. Beane Robert M. Glorioso Richard J. Hollingsworth John W. McCredie Alan G. Nemeth Mahendra R. Patel E. Grant Saviers Victor A. Vyssotsky Gayn B. Winters

The *Digital Technical Journal* is published quarterly by Digital Equipment Corporation, 146 Main Street MLO1-3/B68, Maynard, Massachusetts 01754-2571. Subscriptions to the *Journal* are \$40.00 for four issues and must be prepaid in U.S. funds. University and college professors and Ph.D. students in the electrical engineering and computer science fields receive complimentary subscriptions upon request. Orders, inquiries, and address changes should be sent to the *Digital Technical Journal* at the published-by address. Inquiries can also be sent electronically to DTJ@CRL.DEC.COM. Single copies and back issues are available for \$16.00 each from Digital Press of Digital Equipment Corporation, 1 Burlington Woods Drive, Burlington, MA 01803-4539.

Digital employees may send subscription orders on the ENET to RDVAX::JOURNAL or by interoffice mail to mailstop MLO1-3/B68. Orders should include badge number, site location code, and address. All employees must advise of changes of address.

Comments on the content of any paper are welcomed and may be sent to the editor at the published-by or network address.

Copyright © 1991 Digital Equipment Corporation. Copying without fee is permitted provided that such copies are made for use in educational institutions by faculty members and are not distributed for commercial advantage. Abstracting with credit of Digital Equipment Corporation's authorship is permitted. All rights reserved.

The information in the *Journal* is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in the *Journal*.

ISSN 0898-901 X

Documentation Number EY-H889E-DP

The following are trademarks of Digital Equipment Corporation: ALL-IN-1, DECimage, DECnet, DECprint, DECserver, DECstation, DECwindows, Digital, the Digital logo, LAT, LN03, MicroVAX, PrintServer, Q-bus, ReGIS, rtVAX, ULTRIX, VAX, VAXELN, VAXstation, VMS, VT1000, VT1200, VT1300, and VXT 2000.

Apple DeskTop Bus is a trademark and LocalTalk is a registered trademark of Apple Computer, Inc.

Motorola and 68000 are registered trademarks of Motorola, Inc.

Open Software Foundation is a trademark and OSF and OSF/1 are registered trademarks of Open Software Foundation, Inc.

PostScript is a registered trademark of Adobe Systems, Inc.

Texas Instruments is a trademark of Texas Instruments, Inc.

UNIX is a registered trademark of UNIX System Laboratories, Inc.

X Window System is a trademark of the Massachusetts Institute of Technology.

Book production was done by Digital's Database Publishing Group in Northboro, MA.

#### Cover Design

High-performance screen display of bitonal images is one of the topics in this issue. The bandwriting and manually produced technical drawings on our cover are types of images that can be scanned, stored electronically, and then displayed on an X terminal screen; portions of an image can be enlarged or rotated on screen.

The cover was designed by Sandra Calef of Calef Associates.

# Contents

7 Foreword Larry Cabrinety

Image Processing, Video Terminals, and Printer Technologies

- 9 Hardware Accelerators for Bitonal Image Processing Christopher J. Payson, Christopher J. Cianciolo, Robert N. Crouse, and Catherine F. Winsor

- 26 **X Window Terminals** Björn Engberg and Thomas Porcher

- 36 *ACCESS.bus, an Open Desktop Bus* Peter A. Sichel

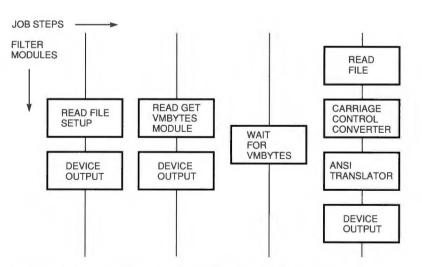

- 43 Design of the DECprint Common Printer Supervisor for VMS Systems

Richard Landau and Alan Guenther

- 55 *The Common Printer Access Protocol* James D. Jones, Ajay P. Kachrani, and Thomas E. Powers

- 61 **Design of the Turbo PrintServer 20 Controller** Guido Simone, Jeffrey A. Metzger, and Gary Vaillette

### Editor's Introduction

Jane C. Blake Editor

Products designed for quality, high-performance presentation of data in both video and hard-copy form are the topics of papers in this issue of the *Digital Technical Journal*. The design challenges range from managing the huge storage requirements of images for display on X terminals to ensuring high-performance in a feature-rich printer environment.

Image processing is the subject of the opening paper by Chris Payson, Chris Cianciolo, Bob Crouse, and Cathy Winsor. The authors note that one advantage of scanning images for screen display is the input time saved; however, the scanned images and data can consume significant amounts of storage space. They then review the development of an image accelerator board that not only helps solve the problem of storage but also addresses the need for high-performance display—view and manipulation—of bitonal images. In addition to specifics of the board implementation, the authors offer an overview of imaging concepts, terms, and future directions for image accelerators.

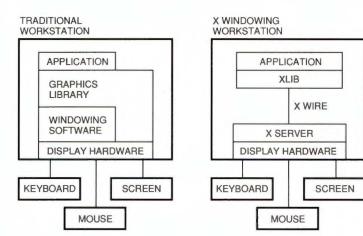

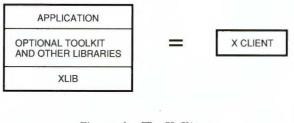

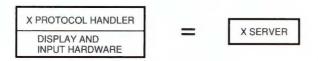

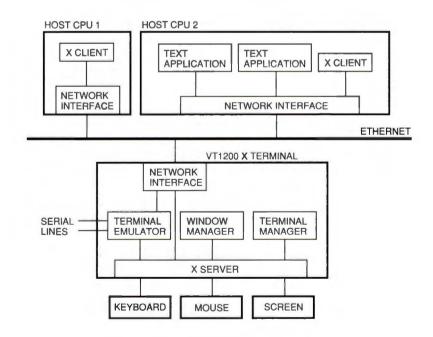

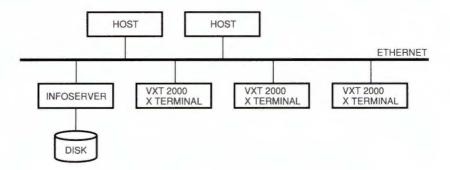

The terminal on which the image accelerator board resides is DECimage 1200, an X terminal. X terminals development in general, including a discussion of the VT1200, is the subject of a paper by Björn Engberg and Tom Porcher. Björn and Tom focus their discussion on a comparison of the X terminal and X workstation environments, and explain why X terminals are a low-cost alternative. The authors present the design choices debated by the engineers during the development of Digital's X terminals, including the selection of a hardware platform, terminal and window management, X server, communications protocols, and font file systems.

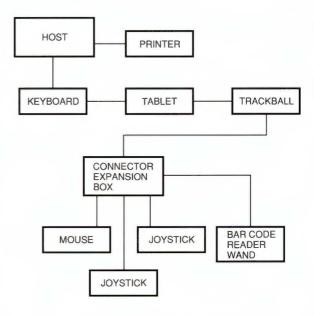

Video terminal and workstation users need the assistance of a number of I/O devices, such as key-

boards, mice, and tablets, all of which may not be made by the same company. A new open desktop bus, described by Peter Sichel, is a simple means to connect as many as 14 low-speed devices to a desktop system. In his paper, Peter presents the project background, reviews the I<sup>2</sup>C technology on which the bus is based, and describes the protocol and the configuration process.

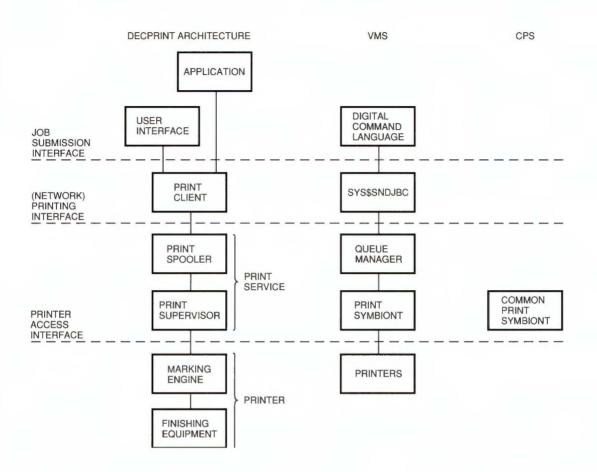

Hard-copy presentation of data and recent developments in printer technologies are the topics of the next three papers. Rick Landau and Alan Guenther review the DECprint Printing Services, which is software that controls numerous printer features for a wide range of printers. Also called a common print symbiont, this component of the VMS printing system supports several page description languages, handles multiple media simultaneously, and uses different I/O interconnections and communication protocols.

Both DECprint Printing Services and the subject of the next paper, the common printer access protocol, are part of the DECprint architecture. The CPAP provides the fundamental services necessary for the presentation of data at the printer. Jim Jones, Ajay Kachrani, and Tom Powers describe the challenges of developing a protocol that operates in a heterogeneous, internetworking environment and that also ensures backward compatibility with older products. Their success in developing a highperformance protocol is evidenced by OSF acceptance of CPAP for inclusion in a future release of OSF/1.

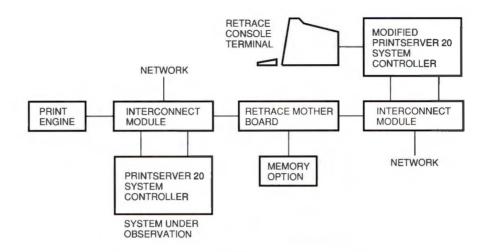

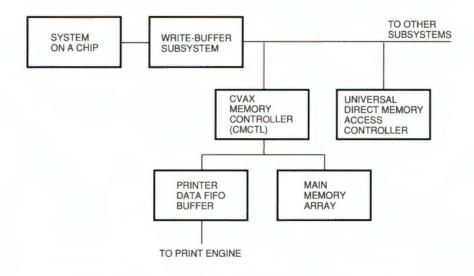

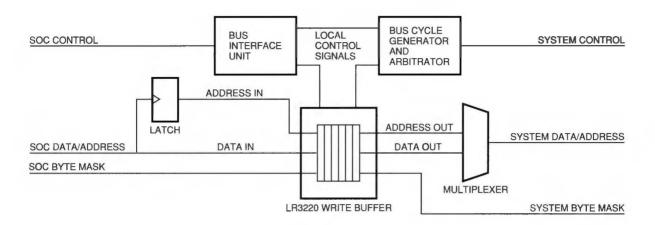

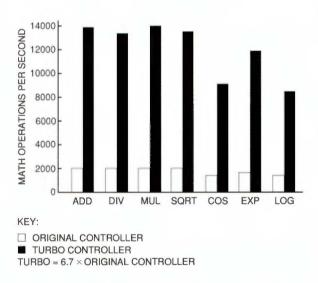

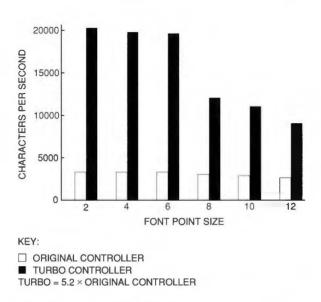

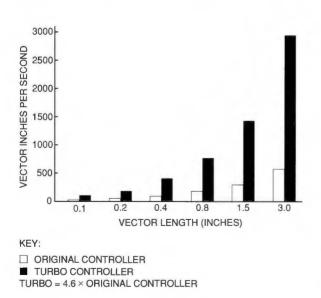

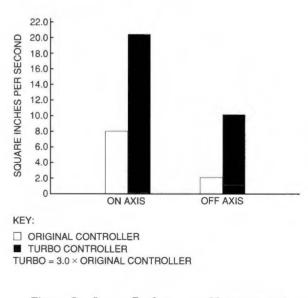

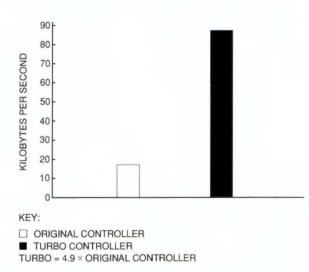

As was the case with the CPAP, performance was also key in the development of the turbo PrintServer 20 controller. Guido Simone, Jeff Metzger, and Gary Vaillette explain that the requirements of complex documents demanded turbo controller performance that was five to eight times that of the current controller. To aid them in making design decisions, a performance analysis tool, RETrACE, was created and is described here. Authors also relate how they used existing chips in order to keep development costs low and still deliver a highperformance controller.

The editors thank Liz Griego-Powell of the Video, Image and Print Systems Group for her help in preparing this issue.

Jane Blake

### Biographies

**Christopher J. Cianciolo** As a hardware design engineer in the Video, Image and Print Systems Group, Chris Cianciolo is currently working on the design for the group's latest imaging product. Chris joined Digital in 1985 after participating in a co-op session in the Power Supply Engineering Group. He also participated in co-op sessions for Charles Stark Draper Laboratory, Inc. on a fiber-optic missile guidance system project. He received his B.S.E.E. from Northeastern University in 1988 and is currently pursuing an M.S.E.E., also from Northeastern.

**Robert N. Crouse** Senior engineer Bob Crouse is a member of the Video, Image and Print Systems Group. He is currently working on the advanced development of new imaging technology for X window terminals. Bob was project engineer for the development of a bitonal imaging accelerator for a low-end VAXstation workstation. As a member of the Electronic Storage Development Group, he designed a double-bit error detection and correction circuit for a VAX mainframe. Bob received his B.S.E.E. from Northeastern University and holds one patent.

**Björn Engberg** As a principal software engineer in the Video, Image and Print Systems Group, Björn Engberg was the main architect and software project leader for the VT1000 and VT1200 X window terminals. He joined Digital in 1978 and worked as a development engineer at CSS in Sweden, where he modified Digital's terminals for the European market. He relocated to the United States in 1982 to work on the VT240, the VT320, the LJ250, and several advanced development projects. Björn received an M.S.E.E. (honors) from the Royal Institute of Technology in Stockholm.

#### Biographies

**A. Alan Guenther** As a member of the technical staff in the DECprint System Software Group, Alan Guenther is involved in the ongoing design and implementation of the DECprint common print symbiont. Prior to this, he was the primary designer and implementor of the distributed queuing services. Alan has worked at Digital since 1973, both as a full-time employee and as an independent consultant (from 1982 to 1990). After receiving a B.S. (honors, 1970) from the University of Montana, he worked at the university until he joined Digital.

**James D. Jones** Jim Jones is a principal engineer in the Hardcopy Systems Engineering Group. He joined Digital in 1974 and was part of a team developing diagnostic programs for the DECsystem-10 and DECSYSTEM-20 systems. After running his own software business for five years, Jim rejoined Digital to design printer controllers and software. Most recently, he provided software for the PrintServer products, authored the Common Printer Access Protocol specification, and is helping to define the next generation of network printers. Jim is a member of IEEE and ACM and participates in the IETF.

**Ajay P. Kachrani** Principal software engineer Ajay Kachrani currently works on the OSF/1 socket and XTI kernel interfaces and security project. Previously, he led the development of the overall PrintServer software version 4.0 with dual network protocol support (DECnet and TCP/IP), from inception through field test. Ajay presented the CPAP protocol as an Internet standard to the IETF and added PrintServer support in version 1.0 of the Palladium Print System at MIT/Project Athena. Ajay holds a B.S.E.E. (honors) from the University of Mysore, India, and an M.S.C.S. from the University of Lowell.

**Richard B. Landau** Richard Landau is the DECprint program manager for the Video, Image and Print Systems Group. Working to improve the interaction of printing software and hardware, he initiated the DECprint, Font, and PostScript programs. Prior to this, Rick was the program and development manager for the VAX DBMS, DATATRIEVE, CDD, and Rdb/VMS products and for the relational database architecture. Before joining Digital in 1974, Rick was an independent consultant and was also employed by Applied Data Research, Inc. He holds A.B. (cum laude, 1969) and M.A. (1973) degrees in statistics from Princeton University.

**Jeffrey A. Metzger** Presently a senior engineer, Jeff came to Digital as a co-op student in 1983, working first in the Semiconductor Engineering Group and then in Hardcopy Engineering. He became a full-time employee after graduating from Cornell University in 1985. He introduced Hardcopy to system-level logic simulation, contributed to the hardware, software, and firmware development of the PrintServer 20, and developed RETrACE, which is used to characterize the execution behavior of PrintServer systems. Jeff is currently working in the Entry Systems Business Group on a next-generation processor product.

**Christopher J. Payson** Chris Payson joined Digital as a hardware design engineer in 1989 after five co-op terms. He is currently working on XIE software and image hardware accelerators. Chris previously worked on performance testing, diagnostics, logic design, and demonstration software, all associated with imaging. He is coapplicant for a patent related to an image clipping algorithm and hardware logic. Chris received a B.S.C.E. from Rochester Institute of Technology with highest honors and is currently pursuing an M.S.C.E. from Northeastern University.

**Thomas C. Porcher** Principal engineer Tom Porcher is a member of the Video, Image and Print Systems Group. He provided technical leadership in the development of the VXT 2000 X terminal. Previously he was a technical leader for the VT240 terminal, VAX Session Support Utility, and the DECterm terminal emulator. Tom holds five patents for work on the VT240 terminal and on the multi-session protocol used in the VT340 and VT400 series terminals. Tom received his B.S. in mathematics from Stevens Institute of Technology (1975). He is a member of the ACM.

**Thomas E. Powers** As a consultant engineer in the Hardcopy Engineering Firmware/Software Group, Tom Powers is a vendor liaison for desktop PostScript printer products. He chairs the DECprint PAP Architecture Team and was a contributor to the PrintServer 40 internal hardware/firmware architecture. Tom represented Digital on American and international standards committees on computer graphics from 1979 to 1989. He led several firmware teams and is coinventor of the ReGIS Graphics Protocol. Tom has a B.S.E.E. from Tufts University and an M.S.E.C.E. from the University of Massachusetts at Amherst.

**Peter A. Sichel** As a principal software engineer in the Video Terminals Architecture Group, Peter Sichel led the development of the ACCESS.bus architecture and device protocol specifications, in addition to writing the initial ACCESS.bus device firmware. He worked on the VT420 video terminal and the DECterm DECwindows terminal emulator, and helps maintain Digital standards for video terminals and keyboards. Peter joined Digital in 1981 after receiving B.S. and M.S. degrees in computer engineering from the University of Michigan.

**Guido R. Simone** Guido Simone is a principal engineer in the Print Systems Engineering Group and was the project leader and architect for the turbo PrintServer 20 controller. He is currently working on the development of a new print system architecture to be used with advanced printing technologies. In previous work, Guido was the project leader and architect for an rtVAX 78R32 CPU chip-based laser printer controller. Before joining Digital in 1980, he received a B.S. in electrical engineering from Rensselaer Polytechnic Institute.

#### **Biographies**

**Gary P. Vaillette** Senior hardware engineer Gary Vaillette has been involved in the design and implementation of printing system hardware since joining Digital in 1983. His current work includes performance characterization of PostScript printers and PrintServer products, and hardware implementation of CCITT decompression in the turbo PrintServer 20 product. Previously, Gary worked at Data General Corporation and helped to develop their token bus network product. He holds an A.A.E.E (1974) from Quinsigamond Community College and expects to receive a B.S.C.S. (May 1992) from Boston University.

**Catherine F. Winsor** As a senior engineer in the Video, Image and Print Systems Group, Cathy Winsor has worked on image accelerators. As the project leader for the DECimage 1200 hardware and the image utility library software, Cathy was involved in the planning and development of an image-capable VT1200. She is currently leading the project to support imaging on the next generation of Digital's X terminals. The project includes an image accelerator board and XIE software. Cathy received an A.B. in engineering sciences from Dartmouth College and a B.S.E.E. from the Thayer School of Engineering.

### Foreword

Larry Cabrinety Vice President, Video, Image and Print Systems Group

For the millions of people worldwide who use Digital's computer equipment, the computer is not the sophisticated system in the back room, or the complex network. It is the equipment they use each day—the terminal or monitor, keyboard and mouse, desktop printer or network printer system.

Today's users demand products with high levels of usability and superior ergonomic features. Digital's products set worldwide standards for the user interface to computer systems. In the 90s our focus is to offer products that operate in multivendor environments with the goal of delivering a complete computing solution. In this issue you will read about some of the Video, Image and Print Systems (VIPS) Group's products and technologies that support network computing and standards-based environments.

Digital entered the video terminal market in 1975 with the VT52 for its time-sharing users. Its replacement, the VT100, embodied two important principles—the use of standards in data communications interchange and the protection of customer investments through backward compatibility of new generations of products. The VT220, introduced in 1983, and the cost-effective VT320 terminals saw the addition of functionality and ergonomic features which established Digital as a leader in the commodities market.

In March 1990, Digital entered the X terminal market with the introduction of the VT1000, followed by the VT1200 and VT1300 terminals later that year. The emergence of MIT's X Window Systems as the accepted industry standard for windowing systems provided a standards-based environment for distributed applications display processing. The X terminal user can now benefit from the graphical user interface, sophisticated applications, and standards of performance previously available only on workstations. X terminals run X11 server code which is operating system independent and ideally suited for heterogeneous, network-based computing environments. In this issue you will read about the engineering decisions made as the X terminals were developed.

There is a growing need in the industry to have imaging applications run alongside conventional text and graphics applications. Technical documentation is an example of this. Imaging applications, however, have special requirements to achieve acceptable end-user performance. Although the X11 software can handle images as bit-map data, software and hardware assistance is required to achieve acceptable performance. Digital has designed DECimage hardware accelerators for rapid processing of image data. This technology is included in the DECimage 1200 and will be incorporated in following generations of X terminals. To make this possible, Digital developed extensions to the X server software that support the high-speed transport and display of image data. To assure open standards, the extensions have been proposed to MIT for incorporation into releases of the X11 server software.

In November 1990, Digital announced its next generation of X terminals. The VXT2000 terminal provides virtual memory and supports both a traditional host-based model with software downloaded to the terminals as well as the server style of X terminal computing.

The VXT2000 terminal was designed to support TCP/IP and LAT protocols, and further demonstrates our commitment to openness and support for customers' multivendor environments. This same philosophy is seen in our printer products and our open desktop bus.

Digital pioneered the distributed printing business with networked laser printers. This product area began when we combined two concepts which had not been combined before—mid-range laser printers and networks. In the mid-1980s most large-scale computing was done on mainframe computers with large printers attached directly to these systems. Typically these dedicated printers were only accessible to users on that particular system. Digital's distributed computing provided an alternative to the mainframe. By combining the power of multiple systems in clusters or on networks, a new distributed large system was created. A printing solution was needed to effectively work in this new distributed computing environment. The PrintServer series addressed this need.

PrintServer products enabled printing resources to be directly connected to networks for the first time, and since they were on the network and not tied to any one system, they were accessible by all systems on those networks. They enabled the complex printer functionality previously found only in dedicated mainframe printers to be distributed throughout end-user environments.

As these mid-range printers migrated out of the computer room and into the office, new demands for functionality were created. Large groups of users brought many different requirements for printing, and our goal was to satisfy as many as possible in a single PrintServer. For example, some people need "A" size paper for office correspondence, while others may need "B" size paper for CAD/CAM or accounting work, and still others need transparencies for presentations. The PrintServer is flexible enough to have all of these different types of media available and offer both simplex and duplex printing.

In 1985 when Digital was first developing the PrintServer, there was no industry standard way of describing the contents of a page to a printer. Each major vendor had its proprietary language, and none offered the compatibility necessary to achieve our print system vision. Our goal was to create a family of products, from large to small, that offered compatibility for all applications. To achieve this goal we had to select a protocol that would enable us to print any file on any printer. At that time Adobe Systems, the developer of PostScript, was a small start-up company in Silicon Valley. PostScript was not a standard, and in fact, only a single PostScript laser printer model had been shipped, the original Apple LaserWriter. Our technical community felt PostScript was the best solution to our needs, and at that point Digital committed to adopting PostScript as our strategic page description language. PostScript printers and PostScript application support are now pervasive throughout the industry and standard printing protocols enable interactive communication with hosts on the network.

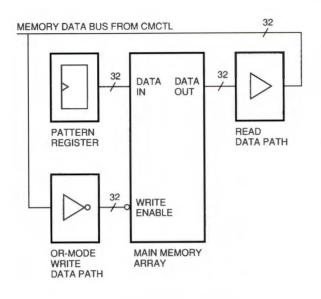

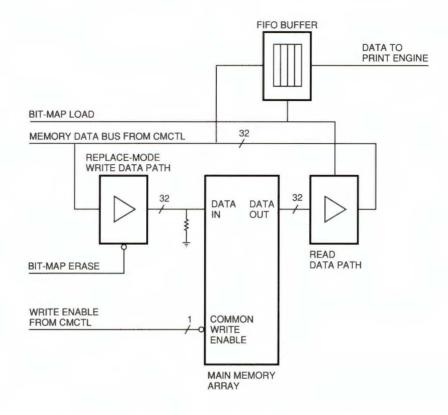

Significant advances have taken place in the PrintServer series over the past seven years. An entire MicroVAX II system was housed within the original PrintServer 40, along with custom hardware acceleration boards developed by the Hardcopy Group to enable printing at 40 pages per minute. In this issue you will read about the singleboard controller that replaces the MicroVAX II and offers far more processing power. Using the latest system-on-a-chip technology, our new turbo board provides leadership performance for our printers. The CCITT image decompression chip enables us to provide full-speed image printing to our customers as the image market develops.

The first PrintServer systems supported printing from VMS hosts over DECnet networks. Since then the breadth of platform support has increased to include first ULTRIX systems and then UNIX operating systems. A software kit for Sun systems will be available soon. In expanding PrintServer connectivity to include UNIX systems and TCP/IP networks, we again faced the problem that no network printing protocol existed for TCP/IP. With the help of Digital's experts at the Western Research Laboratory, we were able to develop a solution. In this issue, we discuss the creation of a network printer access protocol for TCP/IP. Today this network protocol is a proposed standard at the Internet Engineering Task Force, the body controlling the TCP/IP protocol.

The development of the ACCESS.bus product has brought an easy, standard way to link a desktop computer to many interactive user interfaces. This open desktop bus is currently implemented on the Personal DECstation 5000 workstation, and implementations on future RISC workstations and video terminals is underway. Developers of Digital's products will continue to place a high priority on open standards. The papers included in this issue of the *Digital Technical Journal* will provide insight into the key areas of technology used in the design and development of VIPS products.

Christopher J. Payson Christopher J. Cianciolo Robert N. Crouse Catherine F. Winsor

## Hardware Accelerators for Bitonal Image Processing

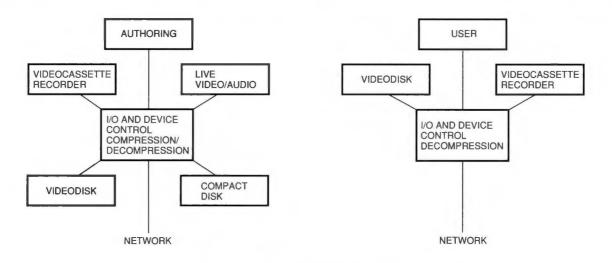

Electronic imaging systems transfer views of real-world scenes or objects into digital bits for storage, manipulation, and viewing. In the area of bitonal images, a large market exists in document management, which consists of scanning volumes of papers for storage and retrieval. However, high scan densities produce huge volumes of data, requiring compression and decompression techniques to preserve system memory and improve system throughput. These techniques, as well as general image processing algorithms, are compute-intensive and require high memory bandwidth. To address the memory issues, and to achieve interactive image display performance, Digital has designed a series of bitonal image bardware accelerators. The intent was to create interactive media view stations, with imaging applications alongside other applications. In addition to achieving memory, performance, and versatility goals, the bardware accelerators bave significantly improved final image legibility.

Bitonal image technology, which can be viewed as the electronic version of today's microfilm method, is experiencing a high rate of growth. However, the electronic image data objects generated and manipulated in this technology are very large and require intensive processing. In a generic system, these requirements can result in poor image processing performance or reduced application performance. To address these needs, Digital has designed a series of imaging hardware accelerators for use in the document management market.

This paper provides a brief tutorial on electronic imaging. It begins with a general description of the imaging data type and compares this type to the standard text and graphics data types. It continues with a discussion of specific issues in bitonal imaging, such as image data size, network transport method, rendering speed, and end-user legibility. The paper then focuses on Digital's DECimage 1200 hardware accelerator for the VT1200 X window terminal developed by the Video, Image and Print Systems Group. It concludes with future image accelerator demands for the processing of multimedia applications and continuous-tone images.

#### Introduction to Imaging

Just as graphics technology blossomed in the 1980s, electronic imaging and its associated technologies

should come of age in the 1990s. Digital imaging is already in use in many areas and new applications are being created for both commercial and scientific markets. The emergence of digital images as standard data types supported by the majority of systems (like text and graphics of today) seems assured. For a greater understanding of specific imaging applications, this section presents general imaging concepts and terms used throughout the paper.

#### **Concepts and Terms**

In its simplest form, imaging is the digital representation of real-world scenes or objects. Just as a camera transfers a view of the real world onto a chemical film, an electronic imaging system transfers the same view into digital bits for storage, manipulation, and viewing. In this paper, the term image refers to the digital bits and bytes that represent the real-world view.

The process of digitizing the view may be done through various methods, e.g., an image scanner or image camera. A scanner is the conceptual inverse of a normal printer. A printer accepts an electronic stream of bits that describe how to place the ink on the paper to create the desired picture. Conversely, optical sensors in the scanner transform light intensity values reflected from a sheet of paper and create a stream of electronic bits to describe the picture. Similar sensors in the focal plane of a camera produce the other common digitization method, the electronic image camera.

The format of a digitized image has many parameters. A pixel is the common name for a group of digitized image bits that all correspond to the same location in the image. This pixel contains information about the intensity and color of the image at one location, in a format that can be interpreted and transformed into a visible dot on a display device such as a printer or screen. The amount of information in the pixel classifies the image into one of three basic types.

- A bitonal image has only one bit in each pixel; the bit is either a one or a zero, representing one of two possible colors (usually black and white).

- A gray-scale image has multiple bits in each pixel, where each pixel represents an intensity value between one color (all zeros) and another color (all ones). Since the two colors are usually black and white, they produce a range of gray-scale values to represent the image.

- A color image has multiple components per pixel, where each component is a group of bits representing a value within a given range. Each component of a color image corresponds to a part of the color space in which it is represented. Color spaces may be thought of as different ways of representing the analog, visible range of colors in a digitized, numeric form. The most popular color spaces are television's YUV format (one gray-scale and two color components) and the bit-mapped computer display's RGB format (red, green, and blue components).

The resolution of an image is simply the density of pixels per unit distance; the most common densities are measured in dots per inch (dpi), where a pixel is called a dot. For example, a facsimile machine (which is nothing more than a scanner, printer, and phone modem in the same unit) typically scans and prints at 100 dpi, although newer models are capable of up to 400 dpi. As another example, most workstation display monitors are capable of 75- to 100-dpi resolution, and some highend monitors achieve up to 300-dpi resolution.

To display an image at a density different from its scanned density, without altering the image's original size, requires the image to be scaled, so that the new image density matches the output media density. Scaling an image may be as simple as replicating and dropping pixels, or it may involve interpolation and other algorithms that take neighboring pixels into account. Generally, the more complex scaling algorithms require more processing power but yield higher-quality images, where quality refers to how well the original scene is represented in the resulting image.

Before an image can be displayed, its pixel values often require conversion to account for the characteristics of the display device. As a simple example, a color image cannot retain its color when output to a black-and-white video monitor or printer. In general, when a device can display fewer colors than an image contains, the image pixel values must be quantized. Simple quantizing, or thresholding, can be used to reduce the number of image colors to the number of display colors, but can result in loss of image quality. Dithering is a more sophisticated method of quantizing, which produces the illusion of true gray scale or color. Although dithering need use no more colors than simple quantizing, it results in displayed images of much higher quality.

Image compression is a transformation process used to reduce the amount of memory required to store the information that represents the image. Different compression methods are used for bitonal images than those used for gray-scale and color images. These methods are standardized to specify exactly how to compress and decompress each type of image. For bitonal images, the most common standards are the ones used in facsimile machines, i.e., Recommendations T.4 and T.6 of the Comité Consultatif Internationale de Télégraphique et Téléphonique (CCITT).<sup>1,2</sup> Commonly known as the Group 3 and Group 4 standards, the designations are often shortened to G3-1D, G3-2D, and G4-2D, referring to the particular standard group and to the coding method, which may be either one- or two-dimensional. For gray-scale and color images, the Joint Photographic Experts Group (JPEG) standard is now emerging as a joint effort of the International Standards Organization (ISO) and CCITT.3 Whichever format or process is used, compression is a compute-intensive task that involves mathematically removing redundancy from the pixel data.

A typical compression method creates an encoded bit stream which cannot be displayed directly; the compressed bits must be decompressed before anything recognizable may be

displayed. The term compression ratio represents the size of the original image divided by the size of the compressed form. For bitonal images using the CCITT standards, the ratio is commonly 20:1 on normal paper documents, but can vary widely with the actual content of the image. The CCITT standards are also "lossless" methods, which means that the decompressed image is guaranteed to be identical to the original image (not one bit different). In contrast, many "lossy" compression methods allow the user to vary the compression ratio such that a low ratio yields a nearly perfect image reproduction and a high ratio yields a visible degradation in image quality. This trade-off between compression and image quality is very useful because of the wide range of applications in imaging. An application need pay no more in memory space and bandwidth than necessary to meet image quality requirements.

#### A New Data Type and Its Features

The image data type is fundamentally different from text and graphics. When a user views characters or pictures on a display device, the source of that view is usually not important. A sheet of text from a printer may have come from either a text file where the printer's own fonts were used, a graphics file where the characters were drawn with line primitives, or an image file where the original text document was scanned into the system. In any case, the same letters and words present the user with approximately the same information; the differences are mostly in character quality and format.

In spite of their large storage space requirements, images have several advantages over graphics or text. First, consider the process of getting the information into the computer. With the imaging process, documents may be scanned automatically in a few seconds or less, compared to the time required for someone to type the information correctly (absolutely no errors) into a text file. Also, even though the software exists to convert electronic raster images into graphic primitive files, the process loses detail from the original image and is relatively slow. Next, consider the variety of information possible on a sheet of paper: a user cannot easily reproduce a diagram or a signature on a document. A scanned image preserves not only the characters, but their font, size, boldness, relative position, any pictures on the page, and even smudges or tears depending on the quality of the image scan.

The major drawback in the imaging process is increased data size, which results in storage memory and network transport problems. High scan densities and color information components create large volumes of data for each image; a bitonal image scanned at 300 dpi from an 8.5-by-11-inch sheet of paper requires over 1 megabyte of memory in its original pixel form. Therefore, compression and decompression are integral parts of any imaging system. Even in compressed form, a bitonal image of a text page requires about 50 kilobytes of storage, whereas its American standard code for information interchange (ASCII) text equivalent requires only 4 to 5 kilobytes. Similarly, a graphics file to describe a simple block diagram is much smaller than its scanned image equivalent.

Based on these advantages and limitations, several applications have emerged as perfect matches for imaging technology. Bitonal images are used in the expanding market of document management, which consists of scanning volumes of papers into images. These images are stored and indexed for later searching and viewing. Basically an electronic file cabinet, this system results in large savings in physical cabinet space, extremely fast document access, and the ability for multiple users to access the same document simultaneously. Gray-scale imaging is often used in medical applications. Electronic versions of X rays can be sent instantly to any specialist in the world for diagnosis, and the ordering of sequential computer-aided testing (CAT)-scan images into a "volume" can provide valuable three-dimensional views. The applications for color imaging are relatively new and still emerging, but some are already in use commercially, e.g., license and conference registration photographs. A further extension to still imaging is digital video, which can be considered as a stream of still images. In conjunction with audio, digital video is commonly known as multimedia, applications for which range from promotional presentations to a manufacturing assembly process tutorial.

In this paper, we focus on the static bitonal imaging method of representing real-world data inside computers. Static imaging is a simpler method of representing a broader range of information than the text and graphics media types, but it carries a greater requirement for processing power and memory space. In addition, static imaging can be viewed as one part of true multimedia, as can text, graphics, audio, video, and any other media formats. Yet static imaging does not have the system speed requirements of a motion video and audio system, which must present data at real-time rates. As long as the user can deal with static images at an interactive rate, i.e., being able to view the images in the format of choice as fast as the user can select them, then static imaging is a powerful media presentation tool. The next section presents the important issues concerning bitonal imaging in a document management environment.

#### **Bitonal Imaging Issues**

As previously mentioned, bitonal electronic imaging as an alternative to paper documents offers many benefits, such as reduced physical storage space, instant and simultaneous access of scanned images, and in general a more accessible media. Serious issues need to be resolved before a productive imaging operation can be implemented. The chief issues are the image data size, transport method, perceived rendering speed, and final legibility. In the following sections, we examine each issue and present solutions.

#### Digitized Image Data Size

The most important issue concerns image data size. Images are typically documents, drawings, or pictures that have been digitized into a computerreadable form for storage and retrieval. Depending on the dot density of the scanner, a single image can be 1 to 30 megabytes or more in size. However, storing a single image in its scanned form is not the typical usage model. Instead, a company may have tens of thousands of scanned documents. Clearly, with today's storage technologies, a company cannot afford to store such a large volume of images in that format.

A typical ASCII file representing the text on an 8.5-by-11-inch sheet of paper requires approxi-

mately 3 kilobytes of memory. If the same sheet of paper is digitized by scanning at various dot densities, the resulting data files are huge, as shown by the decompressed bitonal image sizes in Table 1. Note that Table 2 includes the size of the scanned image if scanned in gray-scale and color modes, although using these modes would not make sense on a black-and-white sheet of paper. The image sizes are included for comparison and are discussed in the section Future Image Accelerator Requirements. The data presented in Tables 1 and 2 illustrates that the size of the original ASCII file is much smaller than any of the scanned versions. The data also gives evidence that scanned images, in general, require considerable memory.

Since the typical use for bitonal images is for volume document archival, an imaging application must include a compression process to reduce memory usage. This process must transform the original scanned image file to a much smaller file without losing the content of the original scanned data.

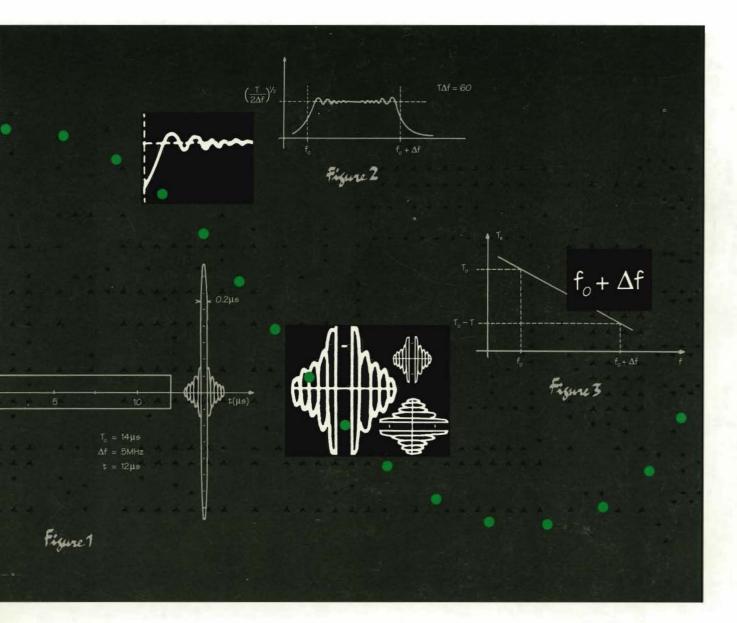

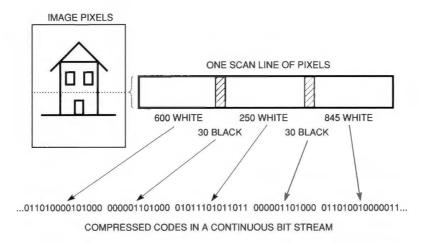

Compression algorithms may take different paths to achieve the same result, but they share one basic process, the removal of redundant information to reduce the object size. A common compression routine searches the pixel data for groupings, or "run lengths," of black or white pixels. Each run length is assigned a code significantly shorter than the run length itself. The codes are assigned by statistics, where the most frequent run lengths are assigned the shortest codes; statistics have been amassed on a variety of document types for different scan densities and document sizes. A compression process parses through the original image file, generating another file that contains the codes representing the original image. Figure 1, a sample bitonal image compression, illustrates these compressed codes in a serial bit stream.

|                                | Scan              | Kilobytes o                  | of Data               |

|--------------------------------|-------------------|------------------------------|-----------------------|

| Document Type<br>(Paper Size)  | Density<br>(dpi)  | Pixel Form<br>(Decompressed) | Typical<br>Compressed |

| A size                         | 100               | 114                          | 46                    |

| (8.5 $	imes$ 11 inch)          | 200<br>300        | 457<br>1027                  | 47<br>50              |

| E size<br>(44 $	imes$ 34 inch) | 100<br>200<br>300 | 1826<br>7305<br>16436        | 106<br>114<br>127     |

#### Table 1 Sample Bitonal Image Sizes

| Hardware Accelerators for Bitonal Image Processing | Hardware . | Accelerators | for | Bitonal | Image | Processing |

|----------------------------------------------------|------------|--------------|-----|---------|-------|------------|

|----------------------------------------------------|------------|--------------|-----|---------|-------|------------|

| Document Type<br>and Size                                    | Kilobytes of Data<br>in Pixel Form<br>(Decompressed) |

|--------------------------------------------------------------|------------------------------------------------------|

| 128 $\times$ 128 pixel, 12 bits per pixel gray-scale image   | 24                                                   |

| 512 $	imes$ 512 pixel, 8 bits per pixel color image          | 256                                                  |

| 512 $\times$ 512 pixel, 24 bits per pixel color image        | 768                                                  |

| 8.5 $	imes$ 11 inch, 100 dpi, 24 bits per pixel, color image | 2740                                                 |

| Table 2 | Sample Gray-scale and Color |

|---------|-----------------------------|

|         | Image Sizes                 |

Several algorithms for bitonal compression are widely used today. As mentioned in the previous section, the most common for bitonal images are the CCITT standards G3-1D, G3-2D, and G4-2D, which all use the approach just described. For the onedimensional method, the algorithm creates run lengths from all pixels on the same scan line. In the two-dimensional methods, the algorithm sometimes creates run lengths the same way, but the previous scan line is also examined. Some codes represent run lengths and even whole scan lines as "the same as the one in the previous scan line, except offset by N pixels," where N is a small integer. The two-dimensional method takes advantage of most of the redundancy in an image and returns the smallest compressed file. In addition to preserving system memory, these compression methods significantly improve network transport performance.

#### Network Transport Constraints

The network transport performance for an image is important, because images are most often stored on a remote system and viewed on a widespread group of display stations. For example, one group in an insurance company receives and scans claim papers to create a centralized image database, while users in another group access the documents simultaneously to process claims. For the imaging system to be productive, this image data needs to be transported quickly from one group to the other: telephone attendants answering calls must have immediate access to the data.

Scanned image documents take a long time to transport between systems, simply because they are so large. When compression techniques are used, a typical uncompressed image stored in 1 megabyte can be reduced to approximately 50 kilobytes. Since transport time is proportional to the number of packets that must be sent across the network, reducing the data size to 5 percent of its original size also reduces the transport time to 5 percent of the original time. Therefore, you can now send twenty compressed images in the same time previously spent sending one uncompressed image.

Even with compression techniques, the image files are still larger than their text file equivalents. Moreover, most network protocols limit their packet size to a maximum number of bytes, i.e., an image file larger than the maximum packet size gets divided over multiple packets. If the protocol requires an acknowledgment between packets, then the transport of a large file over a busy network becomes a lengthy operation.

Figure 1 Bitonal Image Compression

The platform for our most recent accelerator is the VT1200 X window terminal, which uses the local area transport (LAT) network protocol. We soon realized that the X server packet size was limited to 16 kilobytes and the typical A-size compressed document was approximately 50 kilobytes. With this arrangement, each image transport would have required four large data packets and four acknowledgment packets. Working with the X Window Terminal Base System Software Group, we were able to raise the packet size limit to 64 kilobytes. The base system group also implemented a delayed acknowledgment scheme, which eliminates the need for the client to wait for an acknowledgment packet before sending the next data packet. Table 3 shows compressed image data taken during the DECimage 1200 development cycle. Notice that the network transport times for Digital document interchange format (DDIF) decrease sharply after the packet changes.

#### Perceived Rendering Speed

Because the image scanning and compression operations occur only once, they are not as performance-critical as the decompression and rendering for display operations, which are done many times. Decompression and rendering are part of the system's display response time, which is a critical factor in a system designed for high-volume applications that access thousands of images daily. This time is measured from the instant the user presses the key to select an image to view, to the moment the image is displayed completely on the screen. The display response time is a function of the disk read time, network transport time, and display station render time.

Although network transport time and disk file read time have a direct effect on the response time, accelerator developers rarely have any control over them. The disk access time data from the DECimage project analysis shown in Table 3 demonstrates that the disk file read time is a significant portion of the overall response time. Thus, the display station render time is the only area of the display response time which can be clearly influenced and is, therefore, the main focus of our image accelerators. The local processing that must occur at the display station is not a trivial task; an image must be decompressed, scaled, and clipped to fit the user's current window size, and optionally rotated.

The decompression procedure inverts the compression process; both are computationally complex. Input to the procedure is compressed data, and output is the original scan line pixel data, which can be written to a display device. Scaling the data to fit the current window or fill a region of interest is not trivial either: a huge input data stream must be processed (the decompressed, original file), and a moderate output data stream must be created (the viewable image to be displayed). While simple pixel replicate and drop algorithms may be used to scale the data, a more sophisticated scaling algorithm has been shown to greatly enhance the output image quality.

In addition to scaling and clipping, the orthogonal rotation of images (in 90-degree increments) is a useful function on a display station. Some documents may have words running in one direction while pictures are oriented another way, or the user may wish to view a portrait-mode image in landscape mode. In either case, orthogonal rotation can help the user understand the information; i.e., the increased time to rotate the view is warranted.

When an image is scanned, particularly with a hand-held scanner, the paper is never perfectly aligned. Thus, the image often requires a rotation of 1 to 10 degrees to make the view appear straight in the image file. However, multiple users want the

|                           |             |                                              |          |                           | Insport Time<br>econds)    |

|---------------------------|-------------|----------------------------------------------|----------|---------------------------|----------------------------|

| Image Size<br>(kilobytes) | MicroVAX II | Disk Read Time<br>(milliseconds)<br>VAX 8800 | VAX 6440 | After<br>Packet<br>Change | Before<br>Packet<br>Change |

| 19                        | 1223        | 480                                          | 281      | 325                       | 960                        |

| 41                        | 1534        | 655                                          | 332      | 614                       | 1792                       |

| 99                        | 2351        | 1035                                         | 598      | 1351                      | 3928                       |

| 157                       | 3288        | 1380                                         | 716      | 2283                      | 6430                       |

Table 3 DDIF Image File Read Time and File Transport Performance

information from the document as quickly as possible, and should not have to rotate the image by a few degrees to make it perfectly straight on the screen. Therefore, this minimal rotation should be done after the initial scanning process; i.e., only once, prior to indexing the material into the database, and not by every user in a distributed environment. Because any form of rotation is compute-intensive, allowing the user to perform minimal rotations at a high-volume view station would reduce the application's perceived rendering speed and add little value to the station's function.

#### Final Legibility

While the primary issue facing imaging applications is data size, image viewing issues must also be addressed. In short, an effective bitonal imaging display system must be responsive to overall image display performance and the resulting quality of the image displayed. To enhance our products, we optimized the display performance parameters as best we could, given that some parameters are not under our control. Improvements to monitor resolution and scanner densities continue to increase the legibility of images. An affordable image system should increase the image legibility by rendering a bitonal image into a gray-scale image using standard image processing techniques. We discuss the method used in our accelerators, i.e., an intelligent scale operation in the hardware pipeline, in the next section.

#### Hardware Accelerator Design

As explained in the previous section, transforming documents into a stream of electronic bits is not the demanding part of a bitonal imaging process for document management. Also, scanners and dedicated image data-entry stations abound in the marketplace already. Instead, the challenge lies in: (1) managing the image data size to control memory costs and reduce network slowdown; (2) increasing the image rendering speed, i.e., decompress the image, scale it, and clip it to fit the window size with optional rotation; and (3) increasing the quality of the displayed images. This section describes the way our strategy influenced the design of DECimage products. We also discuss the chips used for decompression and scaling, and how Digital's existing client-server protocols support these imaging hardware accelerators.

#### General Design Strategy

The number of applications using bitonal image data continues to increase. In general, these applications attempt to offer low cost while achieving an interactive level of performance, defined as no more than 1 second from point of request to complete image display. Ultimately, software may provide this functionality without hardware acceleration, but today's software cannot. Moreover, the parameters of image systems are not static; scan densities, overall image size, and the number of images per database will all increase. These increases will provide the most incentive for hardware assist at the low end of the X window terminals market, because software alone cannot perform the amount of processing that users will expect for their investment.

*The User Model* Although a single model cannot suit every application, imaging is centered on certain functions. Therefore, a user model built on these functions would be very useful in mapping individual steps to the hardware: hardware versus software performance, the function's frequency of use, and the cost of implementation.

The general user model for bitonal imaging systems is relatively simple. A small market exists for image entry stations, in which documents are scanned, edited, and indexed into a database. While a high throughput rate is important at these stations, a general-purpose image accelerator is not the solution-dedicated entry stations already exist in the market. Instead, we designed a generalpurpose platform, or versatile media view station, to be used for imaging applications alongside other applications. The user model for this larger market is a set of operations for viewing and manipulating images already entered into a database. The most common operations in this model are decompression, scaling, clipping, orthogonal rotation, and region-of-interest zooming.

Display Performance and Quality Optimization The main thrust of the DECimage accelerator is to achieve interactive performance for the operations defined in the user model. A secondary goal is to bring added value to the system by increasing the quality of the displayed image compared to the quality of the scanned image. A side effect of maximizing performance in hardware is that the main system processor has work off-loaded from it, freeing it for other tasks.

The general design of the accelerator uses a pipelined approach. Since maximum performance is desired and a large amount of data must be processed by the accelerator board, multiple passes through the board are not feasible. Similarly, the targeted low cost does not allow a whole image buffer on the board. With one exception (rotation), all board processing should be done in one pipeline, with the system processor simply feeding the input end of the pipe and draining the output end. Because of the large amount of data to be read from the board and displayed on the screen, the processor should only have to move that data, not do any further operations on it. To this end, any logic required to format the pixels for the display bitmap should be included in the pipeline.

Cost Reduction through Less Expensive System Components The net cost of a bitonal imaging system is influenced by the capability of the assist hardware. The capability of the hardware implies flexibility in the choice of other system hardware. In this regard, the most significant impact on cost occurs in the memory and the display. A system that makes use of fast decompression and scaling hardware can quickly display compressed images from memory. This means either more images can be maintained in the same memory, or the system can operate with less memory than it would without the assist hardware; less memory means lower cost.

A more dramatic effect on system cost is in the display. Imaging systems generally need higherdensity displays than nonimaging systems, but the cost of a 150-dpi display is approximately twice the cost of a 100-dpi display of the same dimensions. However, we found that we could increase legibility, i.e., expand a bitonal image to a gray-scale representation, by using an intelligent scale operation in the hardware pipeline. For example, a bitonal image rendered to a 100-dpi display using the intelligent scale process gives the perceived legibility of the same image rendered to a 150-dpi display with a simple scaling method. That is, by adding the intelligent scale, a 100-dpi display can be used where previously only a 150-dpi display would be adequate.

*Cost Reduction through Integration* Presently, as in the DECimage 1200, hardware-assisted image manipulation exists as a board-level option. Higher levels of integration with the base platform will provide lower overall cost for an imaging system. The most straightforward method of integration is to relocate the hardware from the present option to the main system processor board; successive steps of integration would consolidate mapped hardware to fewer total devices. The most costeffective integration will be the inclusion of the mapped hardware in the processor in a way similar to a floating-point unit (FPU). Just as graphics acceleration is now being included in system processor design, images will eventually achieve the status of a required data type and thus be supported in the base system processor.

# *Product Definition—What Does the User Want?*

The previously described strategy was used in the design of the image accelerator board for the DECimage 1200 system. The product requirements called for a low-cost, high-performance document image view station. These requirements evolved from the belief that most users currently investigating imaging systems are interested in applications and hardware that will enable them to quickly and simultaneously view document images and run their existing nonimaging applications. These users are involved with commercial and business applications, rather than scientific applications. The DECimage 1200 system was planned for the management of insurance claims processing, hospital patient medical records, bank records, and manufacturing documents. As previously stated, the imaging functions required for these view-oriented applications are high-speed decompression, scaling, rotation, zooming, and clipping.

#### General Product Design

In defining the image capable system, the key points in the product requirements list were

- High-performance image display

- Low cost

- Bitonal images only (not gray-scale or color)

- View-only functions

The need for high-performance display influenced the project team to design the hardware accelerator board to handle image decompression, scaling, and rotation. Previous performance testing on a 3-VUP (VAX-11/780 units of performance) CPU had yielded image software display times from 5 to 19 seconds. These images were compressed according to the CCITT Group 4 standard (300 dpi, 8.5-by-11 inches), and ranged from 20 to 100 kilobytes in size. In addition, the software display times were highly dependent on the image data content. The more complex image files, which had lower compression ratios, took significantly longer to decompress, scale, and display than the simpler image files. For example, an A-size, 300-dpi, CCITT Group 4 compressed image with a compression ratio of 10:1 took approximately 18 seconds to display, while another with a ratio of 33:1 took approximately 7 seconds.

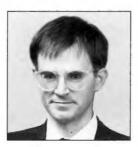

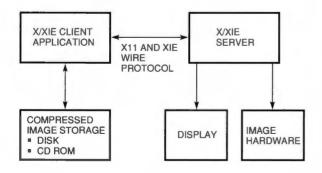

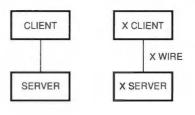

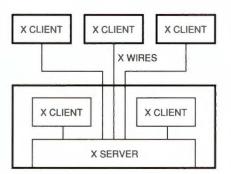

The other three requirements led to decisions about the specific design of the image accelerator board. The need for low cost meant designing an option for an existing low-cost platform, which led us to Digital's VT1200 X window terminal. This requirement also led to our support of the proposed X Image Extension (XIE) protocol.4 The XIE protocol extends the X11 core protocol to enable the transfer of compressed images across the wire and to enable interactive image rendition and display at the server. In the X windowing client-server environment, image applications and compressed image files exist on the client host machine, as depicted in Figure 2. In addition, the XIE protocol standardizes the interface-to-image functions in the X windowing environment and enables the development of a common application that can be used on any XIE-capable station. The client application issues commands to the X server display subsystem and the XIE specialized image subsystem. When a user selects an image to view, the compressed image file is transported from the clientside storage device to the X server memory.

Because the proposed accelerator would handle only bitonal images, we could specialize our board to decompress only the standard CCITT

Group 3 and Group 4 bitonal compression algorithms. This specialization allowed the use of a Digital application-specific integrated circuit (ASIC) decompression chip. Finally, the view-only requirement limited the scope and complexity of the design by eliminating the need for extra hardware to handle the compression of images after they have been scanned and edited.

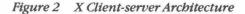

#### Specific Product Design

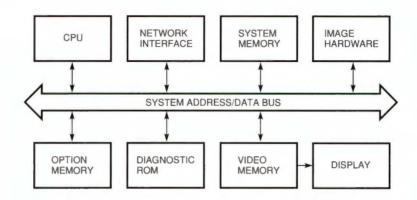

The decisions described in the previous section led to our design of an image accelerator board that supports: CCITT Group 3 and Group 4 image decompression using an ASIC decompression chip; integer scaling using an ASIC scaling chip; orthogonal rotation; and image display. Figure 3 shows a general block diagram of the board and how it fits into Digital's VT1200 system architecture. The accelerator board is attached to the system address/data bus, and its registers, data input port, and data output port are mapped into the CPU's I/O space. The accelerator board is accessed by reading and writing specific addresses like any other system memory space. Note that the image accelerator logic is separate from the video terminal logic. Decompressed images are read from the image board and written to the base system video memory for display.

The main operation consists of the following steps: compressed image data is read from system memory and written to the ASIC decompression buffer by the processor; the data is then decompressed, scaled by the ASIC scaling chip, packed into words, and written to the output buffer. Figure 4 shows a detailed block diagram of the image accelerator board logic. The scaling chip outputs pixels of data (1 bit per pixel in this case) which are packed into words using shift registers. As soon as a word of data is available, the scaling chip output halts. Control signals generated in programmable array logic (PAL) write the packed word into the output buffer and tell the scaling chip to begin outputting pixels again. When the output buffer is full, the processor reads the rendered image data from the buffer. If rotation is required, the processor writes the data to the rotation matrix; otherwise, the data is clipped and written to the bit map. The image driver software, after setting up the board, alternates between checking whether the input buffer is empty and whether the output buffer is full.

Figure 3 VT1200 System Architecture

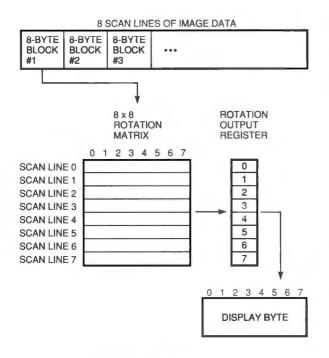

The rotation circuit handles 90- and 270-degree rotation, whereas 180-degree rotation is handled in the data packing shift registers by changing the shift direction. The circuit rotates an 8-by-8-bit block of data at a time. The first byte of eight consecutive scan lines is written into eight individual byte-wide registers. The most significant bit (MSB) of each of these registers is connected to the bytewide rotation output port latch. A processor read of this port triggers a simultaneous shift in all of the rotation data registers so that the next bit of each register is now latched at the rotation output port for the next read. Figure 5 diagrams the rotation circuitry just described.

To achieve the best performance, we pipelined the functional blocks in the hardware. The scaling engine does not need to wait for the entire image to be decompressed before it can begin scaling; instead, scaling begins as soon as the first byte of data is output from the decompressor. Thus different pieces of the image file are being decompressed, scaled, and rotated simultaneously. The hardware pipeline also eliminates the need to store the fully uncompressed image (approximately 1 megabyte of data for A-size 300-dpi images) in memory. The compressed image is written from system memory to the accelerator board and a decompressed, scaled, and clipped image is read from the board. Because of the speed of the hardware, the software can redisplay an image with different scaling, clipping, or rotation parameters; it merely changes the hardware setup for the different parameters and sends the compressed image file back through the accelerator board pipeline.

Figure 4 Block Diagram of DECimage 1200 Accelerator Hardware

#### ASIC Design Description

The ASIC design consists of a decompressor chip, which decodes the compressed image data to pixel image data, and a scaling chip, which converts the image from the input size to the desired display size.

*Decompressor Chip* The decompressor chip acts as a CCITT binary image decoder. The chip contains three distinct stages, which are pipelined for the most efficient data processing. Double buffering of compressed input data is implemented to enable simultaneous input data loading and image decoding to occur. Compressed data is loaded into the input buffer by the processor through a 16- or 32-bit port. Handshaking controls the transfer of decompressed data from the decompressor's 8-bit-wide output bus to the scaling chip.

The first stage of the decompressor chip converts CCITT-standard Huffman codes, which are of variable-length, to 8-bit, fixed-length codes (FLCs).<sup>5</sup> A sequential tree follower circuit is implemented to handle this conversion. Every Huffman code corresponds to a unique path through the tree, which ends at a leaf indicating the FLC. The 8-bit FLC is sent to a first-in, first-out (FIFO) buffer, which holds the data for the second stage.

The second stage of the chip generates a 16-bit, run-length value from the FLC. The lower 15 bits of the word contain the number of consecutive white or black pixels (called the run length). The upper bit of the word contains the run-length color code (0 for a white run and 1 for a black run). An FLC is read from the FIFO buffer and decoded into one of eight routine types. Each routine is made up of several states that control the color code toggling, runlength adder, and accumulator circuits. At the end of each routine, a new word containing the runlength and color information is written into a FIFO buffer for the final stage.

The final stage of the decompressor chip converts the run-length and color information to black or white pixels. This stage outputs these pixels in 16-bit chunks when the scaling chip sends a signal indicating a readiness to accept more data.

Scaling Chip The primary purpose of the scaling chip is to input high-resolution document images (300 dpi) and scale them for display on a mediumdensity monitor (100 dpi). The chip offers independent scaling in the horizontal and vertical directions. The scaling design implemented in the chip is a patented algorithm that maps the input image space to the output image space. General *M*-to-*N* pixel scaling is provided where *M* and *N* are integers between 1 and 127, with the delta between them less than 65. *M* represents the number of pixels in and *N* represents the number of pixels out (in the approximated scale factor).

Given an image input size and a desired display size, we must find the M and N scale factors that best approximate the desired scale factor, within the range limits of M and N as previously stated. Thus an input width of 3300 and a desired output width of 550 are represented by an M of 6 and an N of 1. The approximated M and N values are loaded into the chip scale registers for downscaling or upscaling.

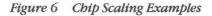

The chip scaling logic uses the scale register values to increment the input pointer position and generate output pixels. A latched increment decision term is updated every clock cycle, based on the previous term and the scale register values. When scaling down (where fewer pixels are output than are input), the logic increments the input pointer position every clock cycle, but only outputs a pixel when the increment decision term is greater than or equal to zero. Figure 6a illustrates how this algorithm maps input pixels to output pixels for a sample reduction. When scaling up (where every input pixel represents at least one output

SCALE DOWN FROM 10 INPUT PIXELS TO 5 OUTPUT PIXELS (M = 2 AND N = 1)INIT = N = 1DELTA1 = 2N = 2DELTA2 = 2N - 2M = -23 6 7 9 10 2 5 8 INPUT 0 . 0 0 INCREMENT DECISION D = 1D = -1 D = 1 D = -1REGISTER OUTPUT 2 0 5 3 (a) Downscaling SCALE UP FROM 3 INPUT PIXELS TO 9 OUTPUT PIXELS (M = 1 AND N = 3)INIT = 2M - N = -1DELTA1 = 2M = 2 DELTA2 = 2M - 2N = -4 2 3 INPUT INCREMENT DECISION D=-3 D=-1 D=1 D=-3 D=-1 D=1 D=-3 D D = 1 REGISTER 0 0 OUTPUT 0 0 2 3 4 5 6 7 8 9

(b) Upscaling

pixel), the logic outputs a pixel every clock cycle, but only increments the input pointer position when the increment decision term is greater than or equal to zero. Figure 6b illustrates how this algorithm maps input pixels to output pixels for a sample magnification. For both cases, the value of the pixel (black or white) being output is the value of the input pixel pointed at during that clock cycle. In this description, simply substitute rows for pixels to represent the vertical scaling process.

#### Software Support for the Hardware

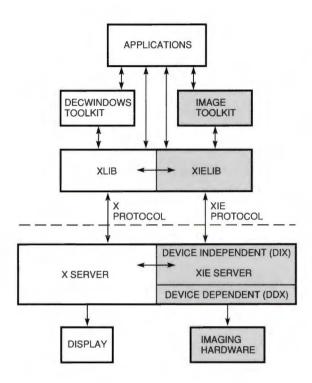

Software support is needed to enhance the functions of the hardware accelerator in our image view station. As mentioned in the section General Product Design, the XIE protocol extends the X11 core protocol to enable the transfer of compressed images across the wire and to enable image rendition and display at the server using the hardware accelerator board. Like the X11 protocol, the XIE protocol consists of a client-side library called XIElib, which provides client applications access to image routines, and a server-side piece, which executes the client requests. The XIE server implements support at two levels: device-independent and device-dependent. The device-dependent level supports the functions that benefit from optimization for a particular platform, or functions that are implemented in hardware accelerators. The device-independent level enables quick porting of functionality from platform to platform. Figure 7 illustrates the X/XIE client-server architecture.

The client-side XIElib offers the minimum functions necessary for image rendition and display. The toolkit level offers higher-level routines that assist with windows application development.

Figure 7 X/XIE Architecture

An example of a routine at this level might be ImageDisplay, which displays an image in a previously created window. ImageDisplay parameters might include x and y scaling values, the rotation angle, and region-of-interest coordinates. Whether programming with the XIE protocol at the library or toolkit level, applications developers benefit from the platform interoperability of the standard interface. Image accelerator hardware and optimized device-dependent XIE code changes the application's image display performance, but an application developed using the XIE protocol can run on any XIE-capable server.

#### Accelerator Performance Results

With the DECimage 1200 X terminal, we have achieved interactive performance rates, reduced memory usage, and increased final image legibility. We achieved these rates by transporting compressed files instead of huge pixel files and by implementing specialized image processing hardware. The DECimage 1200 can read, transport, decompress, scale, and display an 8.5-by-11-inch bitonal document in 1 to 2 seconds. Successive displays, i.e., rotating, region-of-interest zooming, panning around the image, all occur in less than 1 second, which is essentially as fast as the user can ask for the displays. This speed is possible because the image already resides in compressed form in the server memory. Thus, the image does not have to be read from the disk or transported across the network.

#### Future Image Accelerator Requirements

Hardware accelerators will continue to be required for bitonal imaging until software can provide the same functionality at the same performance level. This section discusses the more complex image schemes that are used for gray-scale imaging and multimedia applications. In contrast to bitonal imaging, these applications will require the use of hardware accelerators well into the future.

Other applications will require richer user interfaces utilizing continuous-tone images, video, and audio. All of these new data types are generally data-intensive, and compression or decompression of any one of them is a significant processing burden. Handling them in combination indicates that the need for specialized hardware assistance will persist for the foreseeable future.

#### Continuous-tone Images

Bitonal images are either black or white at each point, but some applications require smoothly shaded or colored images. These images are typically referred to as continuous-tone images, a term that denotes either color or gray-scale, e.g., photographs, X rays, and still video. The representation and required processing of this image format is significantly different from that of bitonal images.

Continuous-tone images are represented by multiple bits per pixel. This format allows a greater range of values for each pixel, which yields greater accuracy in the representation of the original object. Additionally, each pixel can consist of multiple components, as in the case of color. The number of bits used to represent a continuous-tone image is chosen according to the nature of the image.

For example, medical X rays require a high degree of accuracy. Consequently, 12 bits are generally regarded as the minimum acceptable for the rendering of this class of image. Color images typically require 8 bits per pixel for each component (YUV or RGB format) for a total of 24 bits per pixel. Table 2 shows the relative size of samples of each image. The need to express these images in a compressed format is obvious from the storage space requirements and the current storage media limits.

The compression of continuous-tone images can be accomplished in several ways. However, most imaging applications are not closed systems; inevitably, each system needs to manipulate images that are not of its own making. For this reason we adopted the JPEG standard, which specifies an algorithm for the compression of gray-scale and color images. Specifically, the JPEG compression method is based on the two-dimensional (2D) discrete cosine transform (DCT). The DCT decomposes an 8-by-8 rectangle of pixels into its 64 2D spatialfrequency components. The sum of these 64 2D sinusoids exactly reconstructs the 8-by-8 rectangle. However, the rectangle is approximated-and compression is achieved-by discarding most of the 64 components. Typically adjacent pixel values vary slowly, thus there is little energy in most of the discarded high-frequency components.

The edges of objects generally contribute to the high-frequency components of an image, whereas the low-frequency components are made up of intensities that vary more gradually. The more frequency components included in the approximation, the more accurate the approximation becomes. Table 4 shows some sample JPEG image compression ratios.<sup>6</sup>

The most popular part of the JPEG standard, the "baseline" method, was defined to be easily mapped into software, firmware, or hardware. Straightforward DCT algorithms can be efficiently implemented in firmware for programmable DSP chips, due to their pipelined architecture. The first systems to embody the standard did so using DSPs,

| Table 4 | Typical Compression Parameters |

|---------|--------------------------------|

|         | for JPEG                       |

|         |                                |

| Compression<br>Ratio | Compression<br>Method | Rendered Image<br>Integrity                                  |

|----------------------|-----------------------|--------------------------------------------------------------|

| 2:1                  | Lossless              | Highest quality<br>no data loss                              |

| 12:1                 | Lossy                 | Excellent quality—<br>indistinguishable<br>from the original |