# Digital Technical Journal

Digital Equipment Corporation

#### Cover Design

Our cover depicts the dual fiber-optic ring that is the physical medium for high-speed transmission of data in Digital's new FDDI local area network. High-performance workstations, systems, servers, and other LANs can be easily connected to the ring through new bridge and wiring concentrator products, which are among the topics featured in this issue on FDDI.

The cover was designed by Dave Bryant of Digital's Media Communications Group.

#### **Editorial**

Jane C. Blake, Editor Kathleen M. Stetson, Associate Editor

#### Circulation

Catherine M. Phillips, Administrator Suzanne J. Babineau, Secretary

#### Production

Helen L. Patterson, Production Editor Nancy Jones, Typographer Peter Woodbury, Illustrator

#### **Advisory Board**

Samuel H. Fuller, Chairman Richard W. Beane Robert M. Glorioso Richard J. Hollingsworth John W. McCredie Alan G. Nemeth Mahendra R. Patel F. Grant Saviers Robert K. Spitz Victor A. Vyssotsky Gayn B. Winters

The Digital Technical Journal is published quarterly by Digital Equipment Corporation, 146 Main Street MLO1-3/B68, Maynard, Massachusetts 01754-2571. Subscriptions to the Journal are \$40.00 for four issues and must be prepaid in U.S. funds. University and college professors and Ph.D. students in the electrical engineering and computer science fields receive complimentary subscriptions upon request. Orders, inquiries, and address changes should be sent to The Digital Technical Journal at the published-by address. Inquiries can also be sent electronically to DTJ@CRL.DEC.COM. Single copies and back issues are available for \$16.00 each from Digital Press of Digital Equipment Corporation, 12 Crosby Drive, Bedford, MA 01730-1493.

Digital employees may send subscription orders on the ENET to RDVAX::JOURNAL or by interoffice mail to mailstop MLO1-3/B68. Orders should include badge number, cost center, site location code and address. All employees must advise of changes of address.

Comments on the content of any paper are welcomed and may be sent to the editor at the published-by or network address.

Copyright © 1991 Digital Equipment Corporation. Copying without fee is permitted provided that such copies are made for use in educational institutions by faculty members and are not distributed for commercial advantage. Abstracting with credit of Digital Equipment Corporation's authorship is permitted. All rights reserved.

The information in this Journal is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this Journal.

#### Documentation Number EY-H876E-DP

The following are trademarks of Digital Equipment Corporation: CI, DDCMP, DEC, DECbridge, DECconcentrator, DEC FDDIcontroller, DECnet, DECmcc, DECstation, DECWORLD, Digital, the Digital logo, DNA, LAT, ThinWire, TURBOchannel, ULTRIX, VAX, VAXcluster, VMS.

AppleTalk is a registered trademark of Apple Computer, Inc.

C is a registered trademark of Microsoft Corporation.

Motorola is a registered trademark of Motorola, Inc.

SUN is a registered trademark and NFS is a trademark of Sun Microsystems, Inc.

X Window System is a trademark of the Massachusetts Institute of Technology.

UNIX is a registered trademark of UNIX System Laboratories, Inc. Book production was done by Digital's Media Communications Group in Bedford, MA.

## **Contents**

8 Foreword Mark F. Kempf

Fiber Distributed Data Interface

- 10 Fiber Distributed Data Interface Overview William R. Hawe, Richard Graham, and Peter C. Hayden

- 19 **Development of the FDDI Physical Layer**Jerry D. Hutchison, Christopher Baldwin,

and Bruce W. Thompson

- 31 *FDDI Data Link Development* Henry S. Yang, Barry A. Spinney, and Stephen Towning

- 42 An Overview of the Common Node Software Paul W. Ciarfella, David Benson, and David S. Sawyer

- 53 Development of the DECbridge 500 Product Robert C. Kochem, James S. Hiscock, and Brian T. Mayo

- 64 **The DECconcentrator 500 Product**William J. Tiffany, G. Paul Koning, and James E. Kuenzel

- 76 DECelms—Managing Digital's FDDI and Ethernet Extended Local Area Networks

Bruce E. Sweet

- 85 ULTRIX Fiber Distributed Data Interface

Networking Subsystem Implementation

Ursula Sinkewicz, Chran-Ham Chang, Lawrence G. Palmer,

Craig Smelser, and Fred L. Templin

## Editor's Introduction

Jane C. Blake Editor

Digital's fiber distributed data interface, FDDI, is a high-speed LAN that links workstations, systems, and other local area networks such as Ethernet. This new LAN offers distance as well as speed, and extends connections beyond the limits of a building to cover wider areas such as a campus. Papers in this issue of the *Digital Technical Journal* provide insights into the technology choices made during FDDI development and describe the design of the layers and products that make up this 100-megabit/second LAN system.

Among the reasons Digital's engineers chose FDDI technology were its high speed, high throughput, and consistency with existing and evolving standards. In this issue's opening paper, Bill Hawe, Rich Graham, and Peter Hayden review these selection criteria and discuss the reasoning behind the final choices. The authors additionally present an overview of FDDI layers and product operations, which establishes a context for the papers that follow.

The lowest FDDI layer provides the physical connections for data transmission on the fiber-optic ring. In their paper, Jerry Hutchison, Chris Baldwin, and Bruce Thompson describe the operation of the physical layer, the functional partitioning, and the choice of chip set technologies. They then examine the distributed clocking scheme and present the methods used in the design of the optical link (methods later adopted by the Physical Layer Medium Dependent Working Group of the FDDI committee).

Both the development of the physical layer and the next higher layer, the data link layer, resulted in contributions to the ANSI FDDI standard. Digital's implementation of the data link layer is the subject of the next paper by Henry Yang, Barry Spinney, and Steve Towning. In addition to presenting several key algorithms, the authors review the functions of the three data link chips. They conclude their paper with a discussion of chip simulation and test.

Consistent behavior in the physical and data link layers is managed by a set of reusable software libraries called Common Node Software. Paul Ciarfella, Dave Benson, and Dave Sawyer relate the events that led to the development of CNS and describe its functions. CNS implements the protocols defined by the FDDI station management standard and manages the FDDI chip set. CNS is included in the DECbridge and DECconcentrator products.

The DECbridge 500 product is the bridge for traffic between the high-speed FDDI LAN and the slower Ethernet 802.3 LANs. Design considerations and DECbridge functions are presented by Bob Kochem, Jim Hiscock, and Brian Mayo. Their discussion offers insight into the complexities involved in connecting LANs with different data rates, frame formats, and frame sizes.

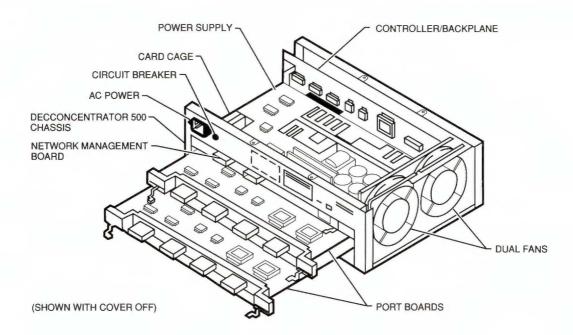

Bill Tiffany, Paul Koning, and Jim Kuenzel then describe the DECconcentrator 500 product. The DECconcentrator, the cornerstone of the FDDI LAN, provides additional ports to which stations can be connected by radially wired cables. The authors examine the significance of Digital's choice of a dual ring of trees topology, which led to the need for a concentrator, and give details of DECconcentrator development.

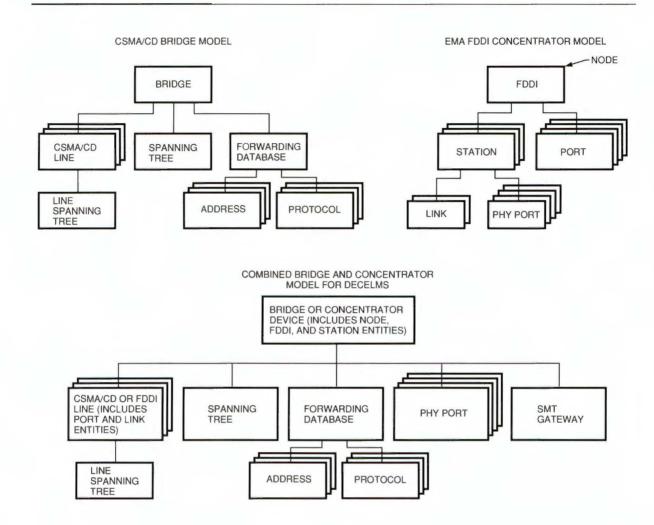

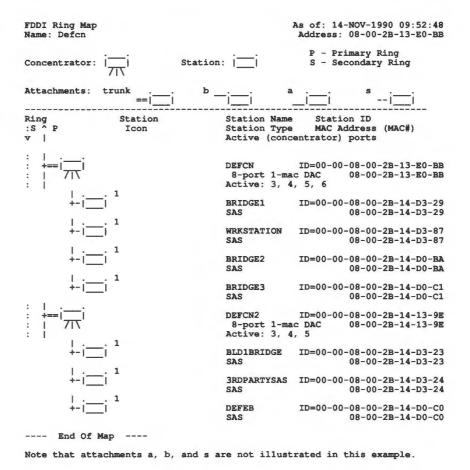

Remote management of the DECconcentrator and DECbridge products, as well as of Ethernet bridges, is provided by DECelms software. Bruce Sweet outlines the challenges DECelms developers faced, including an evolving ANSI FDDI standard and differences between FDDI and Ethernet technologies. He then describes the network management architecture and gives details of features that benefit the network manager.

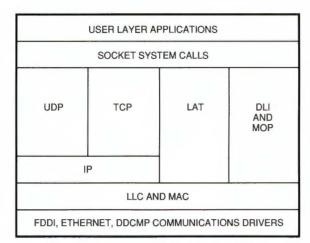

The final paper in this issue addresses the development of an adapter that allows high-performance RISC workstations to connect to FDDI. Ursula Sinkewicz, Chran-Ham Chang, Larry Palmer, Craig Smelser, and Fred Templin review ULTRIX support for the FDDI system and then give details of the DEC FDDIcontroller 700 adapter, which provides a single FDDI attachment for DECstation 5000 workstations. The authors have included discussions of relevant performance data.

The editors thank Mark Kempf for his help in initiating and preparing this issue, and for kindly agreeing to write the issue's Foreword.

Jane Blake

## Biographies

Christopher Baldwin As a principal engineer in the Network Systems Engineering Group, Christopher Baldwin is responsible for the development of the fiber-optic physical layer standard for FDDI (PMD) and helped develop the fiber-optic hardware used in FDDI products. He also worked on fiber-optic transmission for the LAN Bridge 200. Before joining Digital in 1986, Chris was a senior engineer at Polaroid Corporation. He holds a B.A. (1983, honors) in electrical engineering from Brown University and an M.S. (1984) from the Institute of Optics at the University of Rochester.

**David Benson** Software principal engineer Dave Benson is a member of the Communications Systems Engineering Group and the project leader for the Common Node Software. His next responsibility will be as a firmware project leader in the area of future FDDI products. Previously, Dave designed and implemented the physical layer portion of CNS, codeveloped the design verification test (DVT) monitor tool, and was a member of the hardware design team for the FDDI tester. Dave came to Digital in 1986 with ten years' engineering experience from Honeywell Information Systems.

Chran-Ham Chang Chran-Ham Chang is a member of the ULTRIX Network Engineering Group. As a senior software engineer, he is responsible for the ULTRIX FDDI and Ethernet driver design and development. Earlier, Chran was involved in the analysis of ULTRIX network performance and in the design of performance tools. He joined Digital in 1987 after receiving his M.S.C.S. from New Jersey Institute of Technology. Prior to this, Chran worked as a software specialist in Taiwan for the distributor of Digital's products.

**Paul W. Ciarfella** As a software senior engineer in the Communications Systems Engineering Group, Paul Ciarfella is currently developing DECmcc software to manage FDDI networks. Paul was one of the developers of the Common Node Software. Previously, he performed simulation and design verification testing of Digital's FDDI chip set and developed system software for the FDDI tester. Paul joined Digital in 1987 after receiving a B.S.C.S. (high honors) from Northeastern University. He is a co-applicant for a patent related to increasing the robustness of FDDI networks.

**Richard Graham** Richard Graham is a consulting engineer in the Local Area Networks Business Unit. Since joining Digital in 1981, he has worked on a number of projects, including early Ethernet development, the Ethernet repeater, the Ethernet-to-Ethernet bridge (LAN Bridge 100), DEC Standard 134, and most recently, the FDDI-to-Ethernet bridge. Prior to this, Rich was a senior engineer in the Computer System Division of Harris Corporation. He holds a B.S. (1975) in electrical engineering and an M.S. (1977) in computer engineering, both from Syracuse University.

William R. Hawe Senior consulting engineer Bill Hawe manages the LAN Architecture Group. He is involved in designing new LANs and extended LAN technologies. He and his group also design portions of DECnet and TCP/IP architectures. While in Corporate Research, Bill worked on the design of the Ethernet with Xerox and Intel. Since joining Digital in 1980, Bill has done extensive performance analysis and has established this as an integral part of Digital's networking architecture. He holds a B.S.E.E. and an M.S.E.E. He has published 27 papers outside Digital and has 11 patents issued or pending.

Peter C. Hayden Peter Hayden is a principal engineer in the Telecommunications and Networks, Software Development Group. He joined Digital in 1986 as a member of the FDDI team and has contributed to the development of the FDDI technology and product set. He was instrumental in the development of the FDDI test platform which allowed for execution of test programs in both simulation and hardware environments. Peter also led the team that developed the FDDI control software resident in all FDDI products. He holds B.S.E.E. and M.S.C.S. degrees from Union College in Schenectady, NY

James S. Hiscock Principal software engineer James Hiscock is currently a firmware project leader for a future bridge/router product. Prior to this, he led the DECbridge 500 and LAN Bridge 200 firmware projects. He also worked on the UNIBUS-to-Ethernet adapter and the LAN Bridge 100 device. Before coming to Digital in 1984, Jim was employed as a software engineer in the air traffic control division of Raytheon Company. He received a B.S. (1982) in computer systems engineering from the University of Massachusetts.

Jerry D. Hutchison Jerry Hutchison joined Digital in 1977 after receiving B.S. and M.S. degrees in physics, both from Carnegie-Mellon University. As a consulting engineer in the Archicecture and Advanced Development Group, he works on aspects of FDDI technology. Currently an FDDI architect, Jerry was involved in optics development, physical layer and MAC protocols, connection management, and standards. Previously, Jerry designed digital and analog circuitry and worked on Ethernet and computer interconnect products. He holds one patent related to the FDDI physical layer and has four patents pending.

Robert C. Kochem Robert Kochem is an engineering manager in the LAN Interconnect Engineering Group. He was responsible for managing the DECbridge 500 development effort and is presently working on additional LAN interconnect products. In earlier work, Bob led the hardware team that developed the test bed for the FDDI chip set. Before joining Digital in 1986, he was employed by Codex and American Science and Engineering in management positions. Bob holds B.S.E.E. (1972) and M.E.E.E. (1973) degrees from Rensselaer Polytechnic Institute.

**G. Paul Koning** As a consulting engineer in the Distributed Systems Architecture Group, Paul Koning is involved in work related to FDDI architecture, including the specification of Digital's internal architecture and participation in the ANSI FDDI standards development. In this last capacity, he is a representative to the ANSI X3T9.5 standard committee. Since joining Digital in 1978, Paul has also worked on RSTS/E and DECnet/E development projects. He has several patents pending on various aspects of LAN and WAN technology. Paul received a B.S. (1975) in physics from Lawrence University.

James E. Kuenzel As manager of the VAXcluster Systems Engineering consultant team, James Kuenzel is responsible for ensuring that new products and technological directions are well integrated with the existing VAXcluster system. He is currently defining the long-term strategy for the next generation VAXcluster interconnect. Prior to this, Jim was involved in the planning and development of Digital's FDDI product strategy and was a representative to the ANSI FDDI standards committee. Jim is a 1972 graduate of Philco-Ford Technical Institute.

**Brian T. Mayo** Brian Mayo is a principal hardware engineer working in the LAN Interconnect Engineering Group. He was the project engineer for the DECbridge 500 FDDI-to-Ethernet bridge. Previous work includes advanced development efforts in bridging other heterogeneous networks. Before joining Digital, Brian was a product development manager at Gould-Modicon in the Distributed Networking Group. He has also been both a development manager and an operations manager for Teradyne in the Systems Test Division. Brian received his B.S.E.E. (1978) from Cornell University.

Lawrence G. Palmer Larry Palmer is a principal software engineer with the Open Systems Networking Group. He currently leads the MicroKernel advanced development project and has been a member of the ULTRIX team since joining Digital in 1984. Larry is one of the three software developers who initiated the PMAX software project for the DECstation 3100 product by porting the ULTRIX operating system to the MIPS architecture. He received a B.S. (1982) in chemistry with highest honors from the University of Oklahoma and is a member of Phi Beta Kappa.

**David S. Sawyer** In his position as software principal engineer, David Sawyer was the project leader for software development on the DEC FDDIcontroller 700 adapter, common node software, and system software on the FDDI tester. Before joining the Communications Systems Engineering Group, he led efforts for the design verification of the ELM chip, the FDDI physical layer protocol analysis, and the FDDI chip implementation. Dave came to Digital in 1983 after receiving a B.S.E.E. (magna cum laude) from Northeastern University. He is a member of Phi Kappa Phi, Tau Beta Pi, and Eta Kappa Nu.

Ursula Sinkewicz Currently a principal engineer, Ursula Sinkewicz has spent six of her eight years at Digital working on the ULTRIX operating system and communications. She was the project leader for networking changes in ULTRIX symmetrical multiprocessing and worked on the 2780/3780 RJE terminal emulation for the ULTRIX operating system. Ursula holds a B.S. in physics and mathematics from George Washington University and an M.S. in mathematics from Rensselaer Polytechnic Institute. Her master's thesis was a mathematical model for predicting plate subduction near earthquakes.

**Craig Smelser** Craig Smelser is a principal engineer who currently manages the ULTRIX Network Engineering Group. Prior to this, he worked in the Telecommunications and Network Group where he designed and developed the reusble operating system used throughout the FDDI product set. Craig also led the team that delivered the 3270 terminal option for the DECserver hardware. He earned B.S. degrees (1980) in both mathematics and computer science from Geneva College and an M.S. (1987) in software engineering from the Wang Institute of Graduate Studies. Craig joined Digital in 1987.

**Barry A. Spinney** Since joining Digital in 1985, Barry Spinney has been responsible for managing the development of FDDI chips, including the MAC, the RMC, and the CAM. He is currently a consulting engineer in the Distributed Systems Advanced Development Group working on next-generation LAN products. In prior work, Barry was a senior software engineer at Softech, Inc. He holds a B.S. (1979, double honors) in mathematics and computer science from the University of Waterloo and an M.S.C.S. (1981) from the University of Toronto. Barry is a member of IEEE and ACM and has four patents pending.

**Bruce E. Sweet** Bruce Sweet is a software engineering supervisor responsible for the development of network management software for Digital's LAN Bridge and FDDI networking products. In previous work, he was the project leader for the RBMS V2.0 product and for the LAN traffic monitor V1.0 listener software. As an individual contributor to the DECrouter 200 product, Bruce implemented the Ethernet data link and DDCMP protocols and real-time kernel and modem control. He joined Digital in 1983 after receiving a B.S.C.S. from Northeastern University.

Fred L. Templin Fred Templin joined Digital in 1986 and has been a member of the ULTRIX Networks and Communications team until his recent transfer. He was technical project leader for the ULTRIX Ethernet adapter device drivers and for the ULTRIX FDDI engineering effort. Currently, Fred works as a sales support consultant for ULTRIX/Open Systems and networking in the Santa Clara Commercial District Sales Office. He received a B.S.C.S. (1983, University Scholar) and an M.S.C.S. (1986), both from Pennsylvania State University.

Bruce W. Thompson Bruce Thompson is a consulting engineer in the Communications Systems Engineering Group. Since joining Digital in 1985, he has worked on Digital's FDDI chip set and FDDIcontroller 700 adapter for the DECstation 5000 Model 200 workstation. Bruce also helped to define Digital's FDDI wiring concentrator architecture. Previously, he was a principal engineer at Wang Laboratories and Network Switching Systems. Bruce holds a B.S. in electrical and computer engineering from the University of Massachusetts. He has one patent on an aspect of the FDDI physical layer implementation.

William J. Tiffany As a principal engineer in the Network Systems Engineering Group, Bill Tiffany worked on the DECconcentrator 500 project and is currently involved in developing next-generation FDDI products. Earlier, he worked as a diagnostics/hardware engineer on the DECrepeater 200 product. Before coming to Digital in 1986, Bill was employed by Integrity Communications, Raytheon Company, and General Dynamics Corporation. He holds a B.S. (1977) in engineering science from the University of Texas and an M.S.E.E. from the California Institute of Technology.

**Stephen Towning** Principal Engineer Stephen Towning is a member of the Corporate Backbone Systems Group located in Ireland. He has worked in the area of diagnostics and test for 15 years. Steve joined Digital's FDDI program in 1986 as an independent consultant to establish test and verification strategy. He became a full-time Digital employee in 1989. Steve received a B.A. (1975) with joint honors in biology and psychology from Keele University in England. He is a member of ACM and IEEE.

Henry S. Yang As a consulting engineer for the Distributed Systems Architecture Group, Henry Yang's responsibilities focus on the FDDI and Ethernet architectures. Since joining Digital in 1976, he has contributed to the development of the Ethernet adapters, synchronous communication adapters, the LAN address ROM system, Ethernet chips, the FDDI technology and products, and several Digital standards. Henry has 11 patents either issued or pending on Ethernet and FDDI. He holds a B.S.E.E. (1976, honors) from the University of Toronto and an M.S.E.E. (1988) from Northeastern University.

## **Foreword**

Mark F. Kempf Senior Consulting Engineer, FDDI Program Technical Director

In the early 1980s, Digital introduced local area network (LAN) products based on industry-standard, 10-megabit/second Ethernet technology. These products allowed minicomputers, terminal servers, and other network devices to be connected with ease and offered unprecedented bandwidth. As local networks grew in size and began to strain the capabilities of a single LAN in the mid 1980s, Digital introduced products based on the extended LAN concept. By connecting multiple LANs with filtering and forwarding bridges, a much larger number of stations could be interconnected with greater aggregate bandwidth.

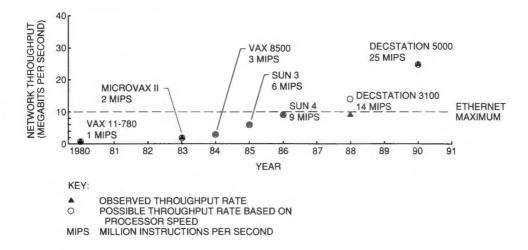

A few years after the introduction of extended LANs, it became apparent that once again the capabilities of existing LANs were being strained, but this time in two dimensions. Not only was there need for greater bandwidth in the "backbone" of the network, but with the advent of much faster workstations and servers, there was need to bring more than 10 megabits/second to a single station. The current and projected performance of workstations indicated that any new generation of LAN suitable for future Digital products would have to offer an order of magnitude increase in bandwidth delivered to a single point. It was also clear that it would have to adhere to a widely accepted industry standard, since users had come to expect the ability to interconnect equipment from many vendors.

After considerable analysis, Digital selected the emerging ANSI FDDI (fiber distributed data interface) 100-megabit/second token ring standard as the basis for our next generation of LAN products. The standard met our important requirements and showed promise of becoming widely accepted

(today, of course, it is). However, because the standard was incomplete, our plans had to accommodate the implementation of specifications that would not always be known at convenient times. Further, because FDDI had not yet been implemented, we had to expect to discover errors in the existing document and to work with the standards organization to correct them. The first group of articles in this issue of the *Digital Technical Journal* describes how we implemented the standard and some of the techniques we applied to deal with change as the standard matured.

Of course, in Digital's business, the implementation of a LAN technology is only a means to an end. The LAN technology must be incorporated into products that provide useful services to our customers. One important product in Digital's initial FDDI offering, the DEC FDDIcontroller 700 workstation adapter, meets the need for more bandwidth delivered to a single station. But LAN users have come to expect more: manageability, interoperability, and a generally radial wiring scheme; and they have large existing LAN infrastructures. Therefore, it was essential to introduce FDDI with a set of products that addressed all these needs as well. Digital's FDDI wiring concentrator, the DECconcentrator 500, permits highly reliable, manageable, radial wiring schemes. DECelms (extended LAN management software) provides network management capability for Digital's FDDI and preexisting extended LAN products.

It is important to remember that Digital does not view FDDI as a replacement for Ethernet, but rather as its complement. The large number of existing Ethernet LANs can be connected to FDDI using another element in Digital's initial FDDI product offering, the DECbridge 500 FDDI/Ethernet bridge. This product allows multiple Ethernets to be interconnected using FDDI as a backbone. Ethernet stations can communicate directly with stations on FDDI as well as with stations on other Ethernets. The second group of articles in this issue describes how we developed these FDDI products.

During the entire development process, we relied on several design strategies. One emphasized the importance of designing the entire system that comprises the product set, not just individual products. Another was the decomposition of problems. Early in the design process, we identified functions that appeared to be independent of others. We took into account how each component that implemented these functions would be used in the various products and how the products would interact with each other. In our development plans, we assumed that once a particular independent component was designed, implemented, and tested, it could be depended on to work as expected when other components were added around it. Naturally, we could not assume that our initial assessment of independence was infallible, and we remained alert for unexpected interactions.

Another related design strategy was partitioning to reduce risk. As mentioned before, the FDDI standard was evolving and subject to change. Therefore, we physically partitioned our design to closely mirror the separate sections of the standards document. This approach helped limit to a single component the impact of standards changes.

The final important design strategy can be summarized as "analyze everything you can, simulate what you can't analyze, and prototype what you can't simulate." The work, expense, and recovery time from errors increases with each step through this progression, and the advantages are obvious. Of course, it is also obvious that this summary is simplistic since it is impossible to analyze, simulate, and prototype exhaustively. It is necessary to step into the gray area of risk assessment and engineering judgment to make satisfactory progress.

FDDI LAN technology development and product development was done in three coordinated and somewhat overlapping phases. In the first phase, we concentrated on analysis and simulation of the underlying FDDI algorithms specified by the standard. We wanted to ensure that they actually described mechanisms that would produce a reliable, high-performance LAN. During this phase we also implemented the standard in silicon and software, and combined these components to form complete FDDI test stations.

Since standards documents, like all written documents, are subject to interpretation, two separate teams were given the task of implementation and verification. We used the test stations, first in a simulation environment, to execute test scripts developed directly from the standards documents to verify standards compliance. The scripts were also used to verify details specific to our implementation and had the additional benefit of making regression testing after incremental changes relatively easy.

In the second phase we concentrated on proving that significant numbers of FDDI stations, which had previously been shown to work individually, could be interconnected to form large reliable rings. This was the most important application of the heavily instrumented test systems. Although analysis and simulation can and did yield important results in this area, the complex interactions between large numbers of asynchronous stations overwhelm both analytical techniques and available computing power.

In the third phase, the focus was on producing products. From a logic design and software standpoint, Digital's FDDI products are largely derived from the test systems used in the previous phases. Of course, laboratory test capabilities were removed and major changes in power and packaging were made; but this approach significantly reduced both the opportunity for introducing new errors and the time to market. We were also able to use the capabilities of the laboratory versions to help verify the correct function of the products.

Numerous other activities that contributed to the effectiveness and timely delivery of the products were carried out simultaneously with engineering design. For instance, Digital maintained a significant presence at the FDDI standards committee to apprise the committee of various technical problems we found in the standard, to offer solutions, and to ensure that our implementation reflected the intent of the standard. In addition, the close working relationships fostered between various organizations, especially between development and manufacturing, resulted in products with a good balance between time to market, function, performance, and manufacturing cost.

The articles in this issue of the *Digital Technical Journal* go into much greater detail on the subjects I have touched on. I hope you find them interesting and informative.

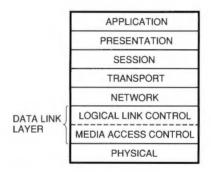

## Fiber Distributed Data Interface Overview

After exploring various alternatives to second-generation local area networks (LANs), Digital selected the fiber distributed data interface (FDDI) system. FDDI implements the International Standards Organization (ISO) physical layer and the media access control sublayer of the data link layer. This system is based on a 100-megabit-persecond fiber-optic ring network and uses a timed-token protocol to coordinate station access to the network. Digital has developed the FDDI base technology, including very large-scale integration (VLSI) chips and software. These chips, licensed to Advanced Micro Devices and Motorola, Inc., provide high-quality alternatives in the market and foster cost reduction. Digital's implementation of FDDI, including backbones in extended LANs, as well as high-speed interconnection of workstations, servers, and central computers, makes available a complete range of system products.

As the use of local area networks (LANs) continues to grow at an exponential rate, many large networks with Ethernet backbones are reaching their usable capacity. In addition, the explosion in the use of high-performance workstations is placing increasing demands on network performance as larger volumes of data pass from station to station. Several years ago, Digital recognized this growth trend and began to plan and develop a second-generation LAN that would follow Ethernet and provide an evolutionary path to higher performance. The selection of FDDI as the second-generation LAN was made with great deliberation. This paper explores the criteria for that choice and the history of the FDDI system to the present. The theory of FDDI operation, the development of the FDDI technology's role in Digital's networks, and the resulting products are also presented and discussed.

#### Selection of FDDI

Many of the same criteria originally used to select Ethernet were again used to evaluate the application environment for the new LAN. The need to consider migration from the popular LANs currently in use presented the only new concern. Paramount among the reasons for selecting the FDDI technology were its tenfold increase in bandwidth over Ethernet, its consistency with other IEEE 802 LANs, and the standardization effort already begun in the American National Standards Institute (ANSI).

It is important when developing a new LAN technology to be sure the differentiation from current capabilities is sufficient to warrant the necessary investment. Moreover, a new LAN is a significant investment for a customer and should offer a large increase in capabilities such as speed and throughput. Without this increase, the technology will have a short life span (a few years) and technology such as parallel use of existing LANs to double capacity will be a realistic alternative to a wholesale replacement of the LAN. However, it is important not to take such a large technological step that exotic and complex implementation constraints become necessary. A LAN that does not lend itself to a very large-scale integration (VLSI) logic solution will not integrate well in the computer interconnect environment and will not be cost effective for wide-scale use.

FDDI, with its tenfold increase in speed, provides significant differentiation from Ethernet/802.3 and current token ring and bus technology to justify the new investment. Examination of the clocking, buffering, and state machine needs of the media access control (MAC) sublayer of the data link layer also showed that the FDDI technology could be implemented in several VLSI chip components. Further, as silicon technology improves, cost reduction is possible, enhancing the longevity of the FDDI LAN technology.

Migration is another important factor in the selection of a new LAN. Many devices exist with

embedded LAN interfaces that will never be directly connected to any other LAN. Still other devices will not benefit from the added capabilities of a higher speed interconnect. Examples of such devices include a processor or workstation too slow to send or to receive data any faster from the network, an output-limited print server, or communications servers with other, more constraining, I/O ports. It would never prove cost effective to upgrade these devices to a new higher speed LAN interface but, as a group, they would need to obtain unconstrained (no bottleneck) connectivity to the services of the new LAN for smooth migration allowing protection of the investment in devices and LANs already in place.

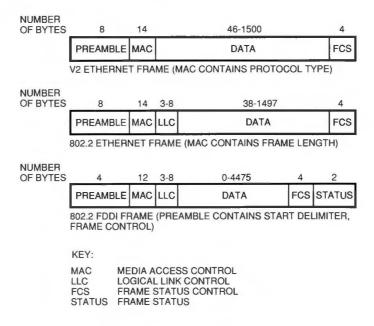

Standards are important for networks as a way to ensure consistent interface compatibility and interoperability for communications services. As the IEEE 802.1d standard readily demonstrates by attempting to interconnect dissimilar LANs at the MAC sublayer, some standards are more compatible than others. A common logical link control (LLC) format or the format within the MAC frame allows a smooth migration between LANs by allowing a transparent bridge to provide protocol-independent translation between LANs. Ethernet, the forerunner of IEEE 802.3, does not use the IEEE 802.2 formatted LLC and, therefore, migration of those frames is more challenging.

Lastly, the media selected for the new LAN has to be consistent with current and projected future needs. Even for slower speed LANs, fiber-optic media is gaining in popularity because of its superior qualities in spanning greater distance, its noise immunity, and its declining user cost.

The FDDI technology meets the necessary selection criteria as an emerging American National Standards Institute (ANSI) standard using fiber and allowing other media in place of fiber while providing a tenfold increase in speed. Migration of some devices could be affected directly by changing controllers, and bridging between LANs could allow smooth migration of all existing devices.

#### FDDI History

Both the ANSI FDDI standards and the industry-wide implementations of these standards have evolved slowly. A variety of factors have contributed to this course of development. The FDDI ring was originally invented at Sperry and Burroughs Corporation. The ring was to be used as a machine room interconnect between processors and storage systems, much like the Computer Interconnect components are used in

Digital's VAXcluster systems.<sup>1</sup> The timed-token, media access control protocol itself was first publicized in 1982 by Bob Grow while he was at Burroughs.<sup>2</sup>

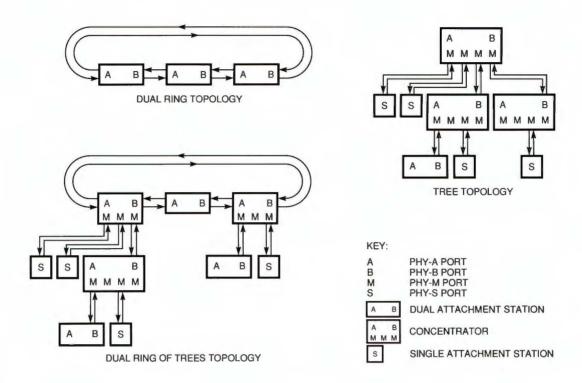

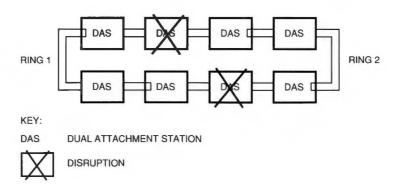

As a machine room interconnect between processors and storage systems, the initial ANSI standard requirements on the FDDI technology were quite different from today's needs. In particular, as a machine room network, the number of stations was assumed to be relatively small compared to a LAN and unstructured cabling was to be used. Since most machines were always running, fault recovery could be accomplished by having a dual ring with failover to the secondary ring. Thus, a failed station or cable could be isolated without partitioning the ring. The FDDI technology retains this property today. However, that basic operation capability is insufficient in a LAN environment with structured cabling requirements and a large number of stations, any number of which might be unplugged or turned off by users. Therefore, we have expanded the definition of the FDDI technology to include such products as concentrators and adapters.

In 1982 the FDDI technology was brought to the attention of the ANSI X3T9 committee, which develops standards for I/O interconnects and channels. Since FDDI was intended to be used as a machine room interconnect, this committee was the appropriate arena for study. Over time, however, as the need for a 100-megabit-per-second LAN emerged, the FDDI technology evolved into a local area network. Some classic standards territory conflicts developed between IEEE 802, the group that defines all the LAN standards, and this ANSI committee.

While FDDI was evolving from a machine room interconnect into a general-purpose LAN, the requirements changed. For a machine room interconnect, some management operation to install and initialize the network might reasonably be allowed. For example, the manager might set the values of various parameters to control the operation and performance of the interconnect network. However, in a general-purpose LAN, manager involvement is unacceptable. For simplicity, robustness, and ease of management, the industry widely accepts that LANs must autoconfigure, also called "plug-and-play." Inevitably, FDDI was required to exhibit the attributes of a true local area network. Since the FDDI technology and standards were already in development when this evolution of requirements occurred, the ANSI committee made an attempt to accommodate the following two views of the network: first, the network should be completely configurable with almost every parameter and policy controlled by management; and second, the network should be a local area network with the corresponding attributes of simplicity and autoconfiguration. Incorporating both models into the ANSI FDDI standards made the standards complex and was one factor contributing to the eight-year-long time period to completion.

### Theory of Operation

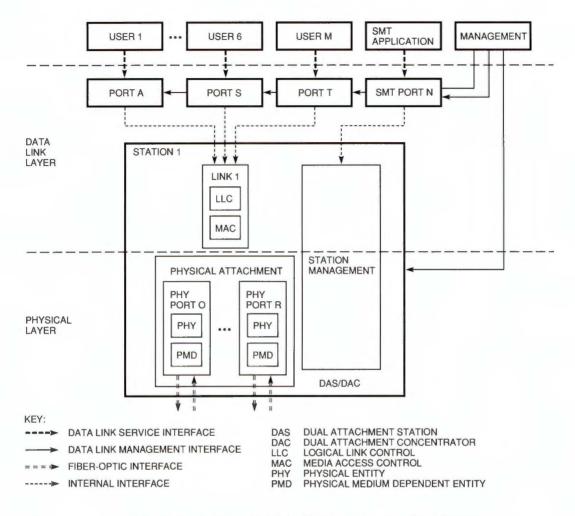

FDDI stations are composed of the basic elements defined by the FDDI standards. The physical medium dependent (PMD) layer specifies the fiber-optic interface and data driver and receiver operation for FDDI stations.<sup>3</sup> The physical layer protocol (PHY) specifies the encoding and framing of data and control information exchanged between stations.<sup>4</sup> The control information exchanged varies with the physical layer protocol type, which is either PHY-A, PHY-B, PHY-M, or PHY-S. The MAC sublayer specifies the protocols for logical ring formation and control, for the transmission and reception of packets at a station, and for the repetition and stripping of packets on the ring.<sup>5,6</sup> Station management (SMT) provides *n*-layer management and a local manage-

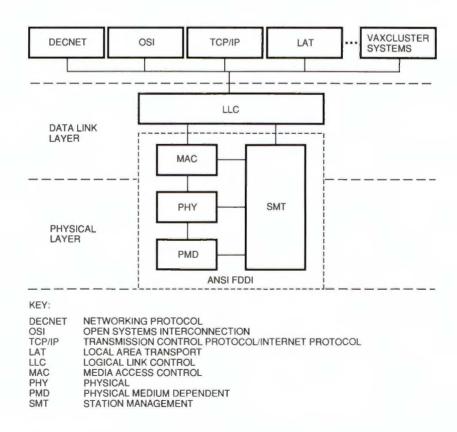

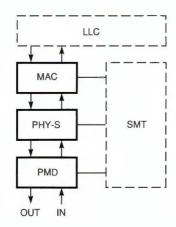

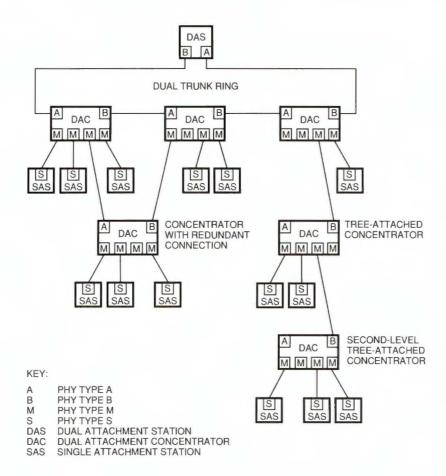

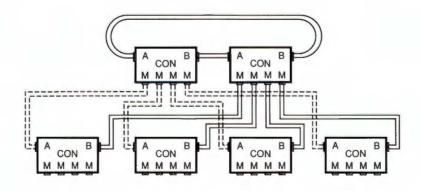

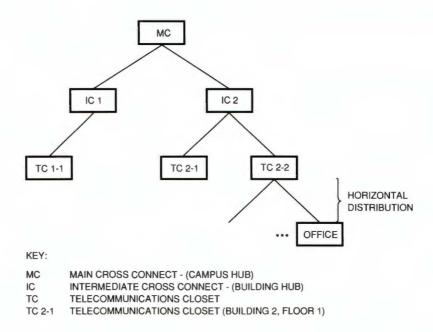

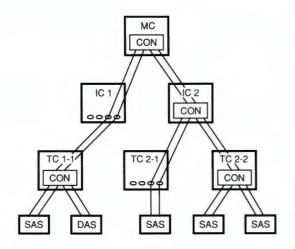

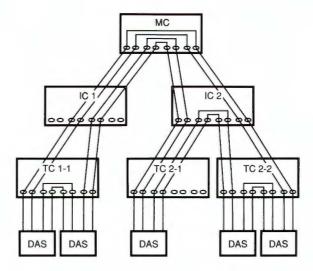

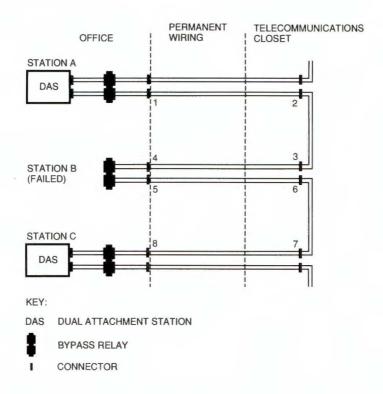

ment interface to the PMD, PHY, and MAC layers. Together these components support an IEEE 802.2-compatible logical link control capable of supporting client protocols such as the Digital networking (DECnet) protocol, open systems interconnection (OSI), local area transport (LAT), and the transmission control protocol/internet protocol (TCP/IP). Stations utilizing the FDDI components can take several forms such as single attachment stations (SASS), dual attachment stations (DASS), and dual attachment concentrators (DACS). An architectural model is shown in Figure 1.

#### Configurations of FDDI Components

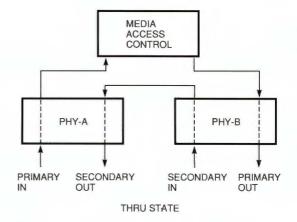

A single attachment station is the simplest configuration and consists of the fundamental FDDI components arranged as shown in Figure 2. There is a single incoming data path and a single outgoing data path with a MAC in between.

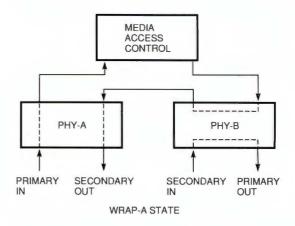

Dual attachment stations, as shown in Figure 3, include a second physical layer and provide connections to a secondary ring for use in the event of breakage on the primary ring. Under fault-free operating conditions represented by the THRU STATE

Figure 1 Architectural Model

Figure 2 Single Attachment Station

area of Figure 3, the primary data path enters through PHY-A, travels through the MAC, and exits through PHY-B. The secondary data path enters through PHY-B and exits directly through PHY-A. If a discontinuity is detected in the primary data path, either within the station or on one of the PHYs, the station wraps the two data paths, thereby providing an alternate route through the secondary data path. This situation is shown in the WRAP A STATE area of Figure 3.

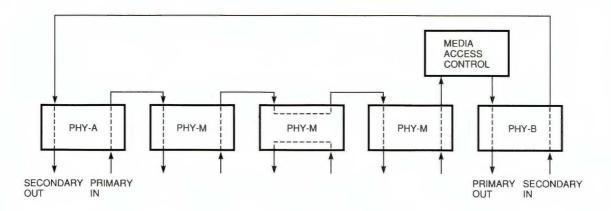

A dual attachment concentrator builds on the dual attachment station by adding additional master PHYs (PHY-M) in the primary data path as shown in Figure 4. Single attachment stations can then be included in the ring by connecting them to the additional PHY-Ms in the concentrator.

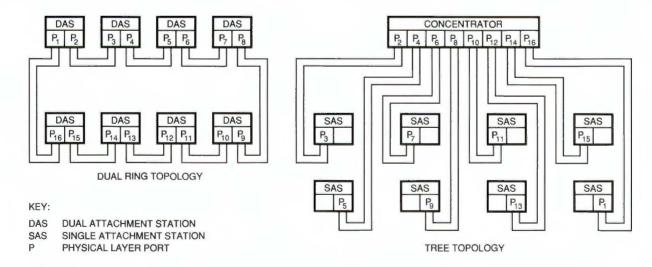

An FDDI LAN is formed by joining multiple stations to form a logical ring topology. The logical ring can take two physical forms, a dual trunk ring and a tree ring.

Figure 3 Dual Attachment Station States

As depicted in the upper portion of Figure 5, the dual trunk ring is formed by connecting dual attachment stations and concentrators to form a LAN. This portion of the LAN consists of two data paths in opposite directions, called the primary

Figure 4 Dual Attachment Concentrator

Figure 5 FDDI Dual Ring of Trees Topology

and secondary rings. Under normal operation, data flows on the primary ring from station to station. In the event of a cable or a station breakage, the stations adjacent to the fault join the primary and secondary rings and then use the secondary path to reestablish a logical ring.

A tree ring can be formed by connecting stations or concentrators to the PHY-Ms of a concentrator as shown in Figure 5. In this formation, the primary data path descends down each branch of the tree passing through each station in the tree, until it finally reemerges into the dual trunk ring.

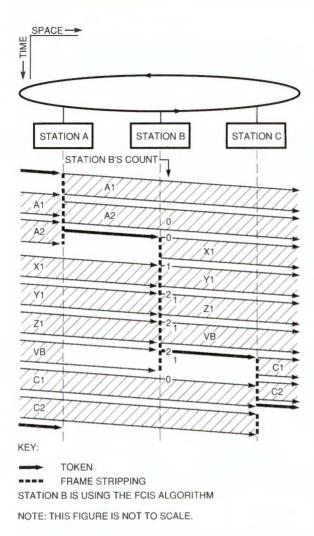

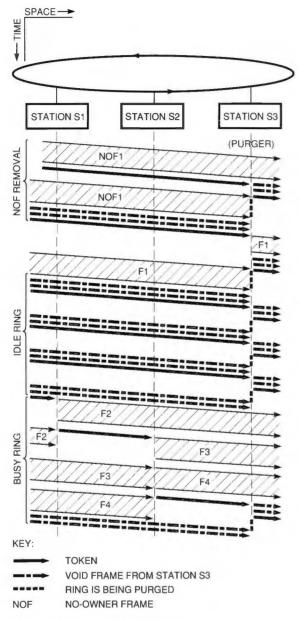

#### Media Access Control Sublayer Operation

As mentioned previously, the MAC sublayer provides the protocols for logical ring formation and data packet operations. To initialize the ring, all MACs first enter the claim process to determine which MAC will generate the token and to establish the token rotation time for the ring. Each station continuously transmits claim frames that contain the

station's requested token rotation time. When a MAC receives claim frames with times shorter than its own, or equal to its own but from a station with a numerically larger address, it yields, stops sending claims, and repeats the claims received from its neighboring station. Eventually the station with the shortest or "winning" time will receive its own claim. This station then generates the token and the ring enters the operational state.

If the claim process does not complete within approximately 100 milliseconds, the MACs in the ring perform a beacon process to confirm continuity of the ring. Special beacon frames are transmitted continuously by all MACs until a beacon is received, at which point it stops transmitting. This process continues until one MAC transmits and receives its own beacon, indicating ring continuity.

To transmit data packets, the MAC first waits for the token to arrive, holds it, and, then, transmits the packets, reissuing a new token at the end of the transmitted packet stream. The time allowance a station has to transmit packets after receiving a token is equal to the token rotation time established by the claim process.

Packets received by a MAC are either repeated for reception by the next station or stripped from the ring. In addition, a MAC may store a copy of a packet for use by the station. After transmitting a frame, a MAC is responsible for stripping that frame from the ring after the frame makes exactly one traversal of the ring. Frames left unstripped are considered no-owner frames and can circulate the ring forever. This condition floods the station to which the frame is addressed and is thus detrimental to ring performance. A MAC typically strips frames by comparing the source address in the frame with the MAC's own address. The MAC strips any frame it has previously sent but repeats the frame, otherwise.

#### FDDI Ring Formation

An FDDI ring is formed in several stages, beginning with the successful establishment of point-to-point links between all adjacent PHYs. These link connections are made by the connection management protocol (CMT).7 This protocol defines control signal exchanges to synchronize the two ends of the link, to exchange information about the PHY type (i.e., A, B, M, S) and link testing requirements of each end to perform link quality testing, and to finalize the connection for normal operation. Before the link establishment enters its final phase, the PHY types of the two ends of the connection are compared, and the connection is allowed if the end types conform to specific connection rules. These rules are carefully established to ensure that rings are configured correctly and to prevent miscabling, which could cause partitioned and unnecessarily wrapped rings. An established link is continually monitored for errors indicated by the reception of improperly encoded data and is shut down if those errors exceed a predetermined threshold.8

After the PHY connection is fully established, the station's MAC is inserted into the ring, and the claim process begins. Digital's stations all use a default requested token rotation time of eight milliseconds in their claim process to ensure a token rotation time, and hence traffic latency, similar to that experienced in other LANs like Ethernet. FDDI provides high aggregate bandwidth and, thus, delivers the low delay essential to many LAN applications such as disk I/O, interactive graphics, and remote procedure calls. Higher settings of the requested token rotation time result in

very large delays on the ring while improving the efficiency only slightly. Therefore, after extensive performance modeling, Digital decided to use this default value for the requested token rotation time. The resulting network operates with low delay and high bandwidth as the default and does not need complicated network management procedures to achieve this level of operation.

Several unique but harmful conditions in FDDI stations must be addressed. Among them are the prevention of and protection against duplicate addresses, no-owner frames, and the stripping of frames sent by bridges or end stations that have multiple addresses.10 Because several of the algorithms fundamental to the operation of the FDDI technology use the stations' addresses, the presence of two stations with the same address causes numerous malfunctions, ranging from beacon-claim oscillations to blocked communications between stations. Frames not properly stripped from the ring can circulate forever, flooding the stations that copy these frames. To protect against strip errors, Digital's chip set has several built-in mechanisms. Digital also greatly improved the data integrity of the ring. This improvement is particularly important to token ring architecture where messages traverse virtually all of the links in the network before arriving at their destinations. Robustness in the face of link bit errors becomes extremely important. Digital designed several improvements to the basic FDDI algorithms, and the ANSI committee adopted them to improve the undetected error rates on a network.11

#### Role of FDDI in Digital's Networks

The FDDI technology is more than just another data link interface that allows the use of transmit and receive fibers between devices. Digital's decision to embark on the FDDI development effort was a major program undertaking involving the development of VLSI chips and, subsequently, FDDI software and hardware products. Although the development of chips may seem to be at the heart of the FDDI program, chips are certainly not the products that help customers solve problems. Chips comprise only a small portion of each large printed circuit board, but this portion is an important one.

Before focusing on chip development, Digital carried out a large simulation effort to ensure the ANSI standards were correct and complete. Once the standards were verified, modeling was performed to produce chips that met these standards. Allowances and trade-offs were made for unfinished

sections and future standards migration. Real products were then planned around the chips as the use of FDDI was threaded into Digital's network architectures and existing products. An implementation strategy for each product was then formulated to balance the risks, the resources, and the timeliness of customer needs.

It was important for Digital to understand migration of current products and to think forward to the needs beyond the initial program goals. LAN management and host connections take the FDDI technology beyond a simple high-speed backbone for the extension of bandwidth-limited existing LANs. Because Digital considered the FDDI technology beyond its use as just another new data link, this technology is the natural choice as the next step in network evolution.

At the onset of Digital's FDDI program, and at several points during its development, a number of key program-wide decisions and policies were adopted. The commitment to simulation, both in breadth (e.g., chip design, board design, and software) and extent (e.g., behavioral models, gate-level models, integration of operational software with simulation models) was essential to the success of the FDDI technology development. All the chips developed were fully functional in their first pass in silicon, and the integration of the controlling and test software with the chips was fast and smooth.

Given the extensive investment in ensuring correctness of the FDDI technology, all FDDI products were to use the same FDDI building blocks, including the chips and controlling software.<sup>12</sup> Such sharing and reuse of investment eliminated the duplication of effort, guaranteed the consistent operation of all products, and shortened the time to market. To ensure an even broader use of this technology, major portions were made available on the open market.

Another key program decision was the adoption of electrically alterable read-only memory (EAROM) in place of traditional read-only memory (ROM) to store the firmware in each product. SMT, which is implemented almost entirely in firmware, was a rapidly evolving specification while the products were under development. To accommodate these ongoing changes and the threat of change after product shipment, EAROM was included in all products to allow firmware to be updated remotely over the network. As a result, EAROM reduced the cost of product enhancement by eliminating the need to change ROM in the field or swap out boards and rework them at the factory.

### Deployment of FDDI

As a baseline effort in deploying FDDI in products, Digital developed the FDDI design corner shown in Figure 6, consisting of chips and FDDI control firmware for use in all applications of FDDI. In addition to using the design corner in all of Digital's products, two of the chips critical to FDDI interoperability, the MAC and the ELM, together with the SMT firmware, which controls the chips and the behavior of the station, were licensed to Advanced Micro Devices and to Motorola, Inc. for manufacture and sale on the open market. Widespread availability of this technology will foster competition to drive down cost and increase levels of interoperability and consistency among FDDI implementations.

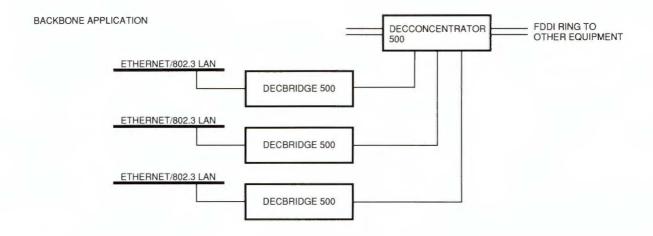

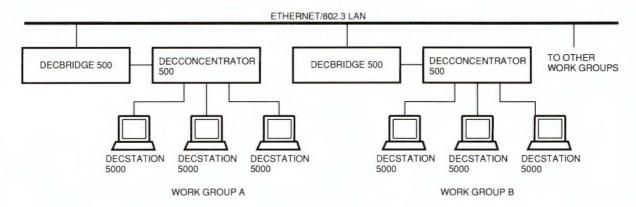

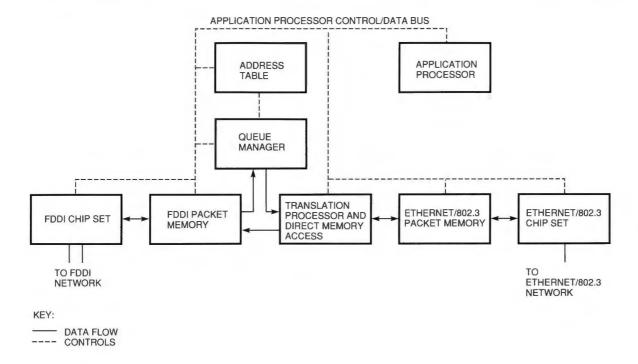

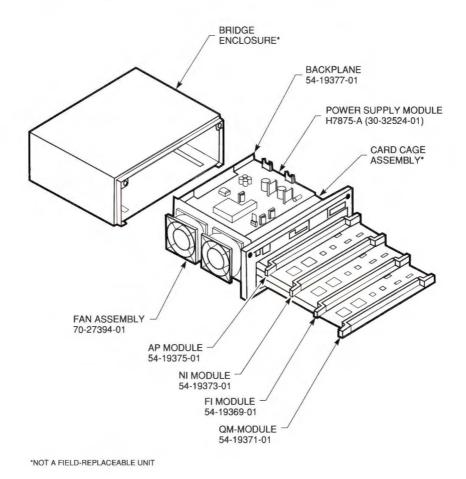

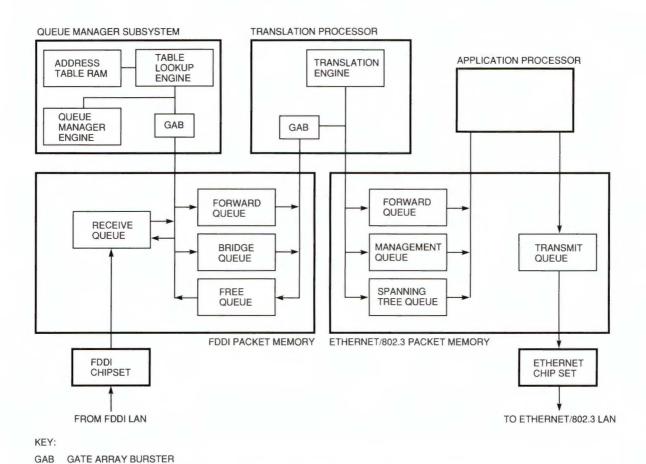

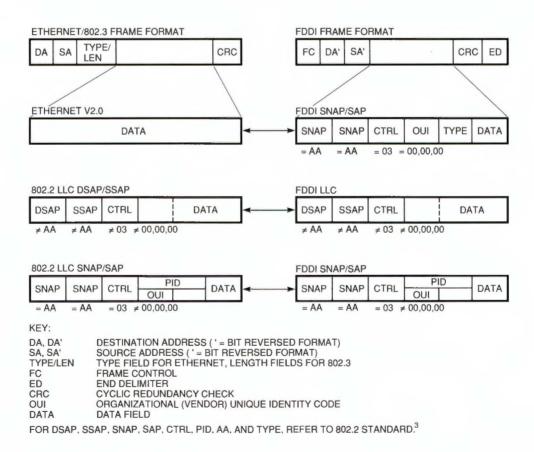

## FDDI-to-Ethernet Bridge

The Ethernet/802.3 bridge to the FDDI network is an important device in the first product set offered for FDDI connectivity. The DECbridge 500 product provides the smooth migration of all Ethernet and IEEE 802.3 devices currently in the marketplace to the increased backbone bandwidth of the FDDI technology. Most local networks are LAN-based

Figure 6 FDDI Design Corner

CLOCK AND DATA CONVERSION TRANSMITTER

CLOCK AND DATA CONVERSION RECEIVER

CDCT

with the LANs being interconnected to form extended LANs by the use of bridges. The bridges are transparent to all users' protocols on the LANs. This capability for transparent interconnection is one of the keys to the instant use of and easy migration to the added bandwidth and other benefits of FDDI. However, providing the transparent interconnect is difficult. Frame formats, bit ordering, padding fields, and even the length of the packets differ between the Ethernet and IEEE 802.3 LANs. These differences force the frames to be translated as they pass through the DECbridge 500 device. This translation, coupled with a stiff requirement for data integrity for the MAC bridging standard IEEE 802.1d and the performance needs of dealing efficiently with packet rates approaching 500,000 per second, created a formidable design task.13

#### **FDDI Concentrator**

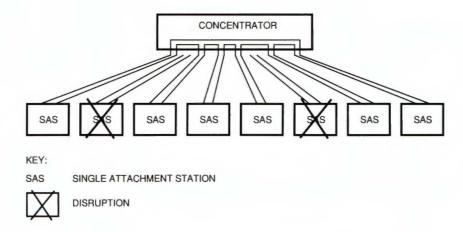

To make the FDDI technology widely acceptable as the next generation LAN, several of the logistical obstacles inherent in a ring topology had to be overcome. Connecting new stations to a LAN can be frequent events. These events must not be restricted or cause a disruption if the LAN is to be truly usable. The nature of a ring topology causes the network to break whenever a station is removed or while a station is being inserted. The dual ring accommodates one such event by wrapping at the adjacent stations, but two or more such events are disastrous because they partition the network into isolated parts. A concentrator can solve this problem by connecting to a station, testing the link between the station and the concentrator, and then splicing the new station into the ring with minimal disruption. At the same time, a concentrator can automatically drop a station out of the ring should the station malfunction or lose power.

In addition to the obstacle of connecting new stations, it is inconvenient to map a ring topology into star wiring, which is well known and widely used for its convenience and manageability. Concentrators can turn a logical ring into a hierarchical starwired network, thus solving this mapping problem.

Digital's DEC concentrator 500 product was built to support simple installation and network configuration, existing building cabling plants, and the cost savings and simplicity of single attachment stations. This FDDI concentrator is low cost and flexible, with a dual attachment and up to eight master ports for connecting single attachment stations or additional concentrators into the ring. With the concentrator, any of the described FDDI topologies

can be created to best suit a customer's cabling, network management, and availability needs.<sup>14</sup>

### FDDI for Workstations

Digital designed a simple high-performance FDDI adapter for TURBOchannel workstations and servers in conjunction with the design of the DECstation 5000 reduced instruction set computer (RISC)-based system.<sup>15</sup> The aim of this product was to produce an FDDI interface that was both inexpensive and high performance. With this adapter and ULTRIX operating system support, Digital attempted to address many of the shortcomings that have plagued most adapters and operating systems attempting to achieve high performance.<sup>16</sup>

The applications of the FDDI technology for workstations and servers depend on the particular choice of user applications and on the network configuration. One application is the use of the FDDI technology for a work group of high-performance workstations and servers. Some high-performance I/O-intensive applications need more bandwidth than a large, shared Ethernet can handle. As a result, a work group may form around an FDDI network. One application example is called visualization, where a large volume of real-time graphics or imaging information is transmitted over the network from a compute server. Various applications of digital image transmission have few real-time latency requirements, but still require a large bandwidth.<sup>17</sup>

Another application of the FDDI technology in workstation environments is to achieve higher bandwidth for server/server and backbone interconnection. A shared Ethernet for client/server as well as server/server communications can be overloaded, particularly if the population of servers or workstations is large. FDDI can be used as a backbone to provide higher bandwidth between the servers. Alternatively, the network may be a hybrid, where the FDDI network is used for high client/server bandwidth by some systems and for high server/ server bandwidth by others. Hybrid networks often have multiple FDDI networks and multiple Ethernet networks. This configuration is typical of evolving extended LANs, as new technology such as FDDI is added into the existing network infrastructure.

#### FDDI in the Future

As a new technology, FDDI has a long future with opportunities for greater levels of circuit integration, lower cost designs, and alternative media types to match the wide range of possible applications. Significant progress has already been made

in this direction with the introduction of the DECcontroller 500 adapter, the most compact, least expensive, and one of the highest performing workstation adapters in the industry today. In addition, the ground-breaking technical work and standards committee activity regarding various types of copper media offers tremendous opportunities for cost reduction which will enable broader utilization of the performance offered by the FDDI technology.<sup>18</sup>

In addition to the original physical medium dependent standard specified by ANSI for FDDI, an additional standard has been developed for operation on single-mode fiber over distances up to 30 kilometers (km). This standard will be particularly useful in deploying an FDDI network that must span one or more distances greater than 2 km such as a campus backbone. Other medium types are currently under investigation to provide optimization in areas such as cost and ease of installation.

### Acknowledgments

We would like to thank the Telecommunications and Networking LAN Architecture and Development teams. Without their hard work none of the many technical advances made in bringing the FDDI technology to market would have been possible. We would also like to thank Bob Krueger for his role in successfully leading the entire program. Finally, we would like to thank Mark Kempf, Paul Koning, and Tony Lauck for their timely review of this paper.

#### References

- 1. N. Kronenberg, H. Levy, W. Strecker, and R. Merewood, "The VAXcluster Concept: An Overview of a Distributed System," *Digital Technical Journal*, vol. 1, no. 5 (September 1987): 7-21.

- 2. R. Grow, "A Timed Token Protocol for Local Area Networks," *Proceedings of IEEE Electro/82 Conference*, Boston, MA (May 25–27, 1982).

- 3. Token Ring Physical Layer, Medium Dependent (PMD), (International Standards Organization, reference no. ISO 9314-3, 1990).

- 4. *Token Ring Physical Layer Protocol,* (International Standards Organization, reference no. ISO 9314-1, 1989).

- 5. *Token Ring Media Access Control (MAC)*, (International Standards Organization, reference no. ISO 9314-2, 1989).

- 6. H. Yang, B. Spinney, and S. Towning, "FDDI Data Link Development," *Digital Technical Journal*, vol. 3, no. 2 (Spring 1991, this issue): 31-41.

- 7. FDDI Station Management (SMT) Preliminary

- Draft Proposed American National Standard, ANSI X3T9/90-X3T9.5/84-49, REV 6.2 (May 1990).

- 8. J. Hutchison, C. Baldwin, and B. Thompson, "Development of the FDDI Physical Layer," *Digital Technical Journal*, vol. 3, no. 2 (Spring 1991, this issue): 19–30.

- R.Jain, "Performance Analysis of FDDI Token Ring Networks: Effect of Parameters and Guidelines for Setting TTRT," DEC-TR 655 (Maynard: Digital Equipment Corporation, September 1989).

- 10. H. Yang and K. Ramakrishnan, "Frame Content Independent Stripping for Token Rings," *Proceedings of the ACM SIGCOM '90 Symposium* (1990): 276–286.

- 11. R. Jain, "Error Characteristics of Fiber Distributed Data Interface (FDDI)," *IEEE Transactions on Communications*, vol. 38, no. 8 (August 1990).

- 12. P. Ciarfella, D. Benson, and D. Sawyer, "An Overview of the Common Node Software," *Digital Technical Journal*, vol. 3, no. 2 (Spring 1991, this issue): 42-52.

- 13. R. Kochem, J. Hiscock, and B. Mayo, "Development of the DECbridge 500 Product," *Digital Technical Journal*, vol. 3, no. 2 (Spring 1991, this issue): 53–63.

- W. Tiffany, P. Koning, and J. Kuenzel, "The DECconcentrator 500 Product," *Digital Technical Journal*, vol. 3, no. 2 (Spring 1991, this issue): 64-75.

- 15. U. Sinkewicz, C. Chang, L. Palmer, C. Smelser, and F. Templin, "ULTRIX Fiber Distributed Data Interface Networking Subsystem Implementation," *Digital Technical Journal*, vol. 3, no. 2 (Spring 1991, this issue): 85–93.

- 16. W. Hawe and K. Ramakrishnan, "The Workstation on the Network: Performance Considerations for the Communications Interface," Proceedings of the Second Workshop on Workstation Operating Systems, Asilomar Conference Center, CA (September 1989).

- 17. K. Ramakrishnan and W. Hawe, "Performance of an Extended Local Area Network for Image Applications," *Proceedings of the Fifth Annual Phoenix International Conference on Computers and Communications*, Scottsdale, AZ (March 26–28, 1986).

- 18. S. Ginzburg, W. Mallard, and D. Newman, "FDDI over Unshielded Twisted Pairs," *IEEE Proceedings, Eighteenth Conference on Local Computer Networks* (October 1990).

## Development of the FDDI Physical Layer

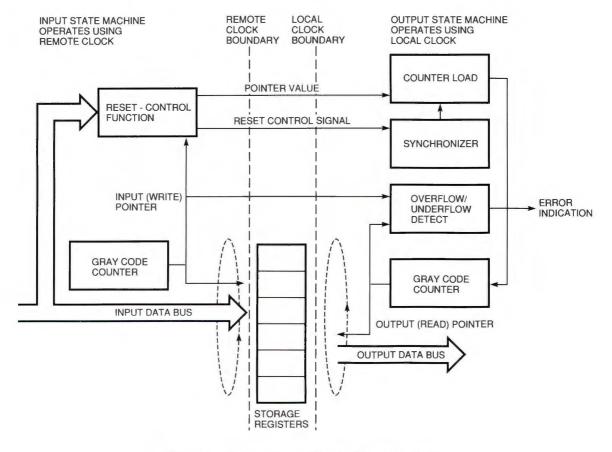

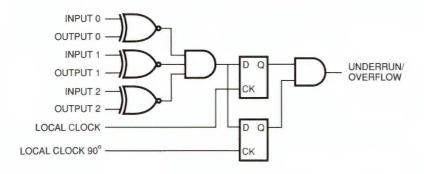

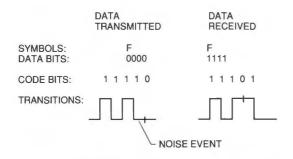

The engineering development of the FDDI physical layer resulted in the delivery of components, specifications, and protocols. The development presented new design problems related to the technology and to the operation of token rings. The choice of the most appropriate technologies for the chip set was based on technology issues, risk control, and costs. The chip set that emerged after the physical layer functions were partitioned uses both ECL and CMOS technology. Further, three design problems of general interest arose during development: the elasticity buffer and circuitry related to the distributed clocks in an FDDI LAN, the multimode fiber-optic link using light emitting diodes, and the media error processes as related to correctness and fault isolation.

The fiber distributed data interface (FDDI) is a multiaccess, packet-switching local area network (LAN) that operates at 100 megabits (Mb) per second. The physical layer of FDDI—the topic of this paper connects many stations, each of which may transmit information to any other station in the network. As in other LANs, packets of user data are encoded according to the physical layer protocol and are transmitted as a serial data stream over a physical media to other stations of the LAN. FDDI, however, is unique in its use of hundreds of individual, pointto-point, fiber-optic connections that form a ring network in the physical layer. The resulting LAN offers both a high data rate and a total physical extent of up to 100 kilometers (km).

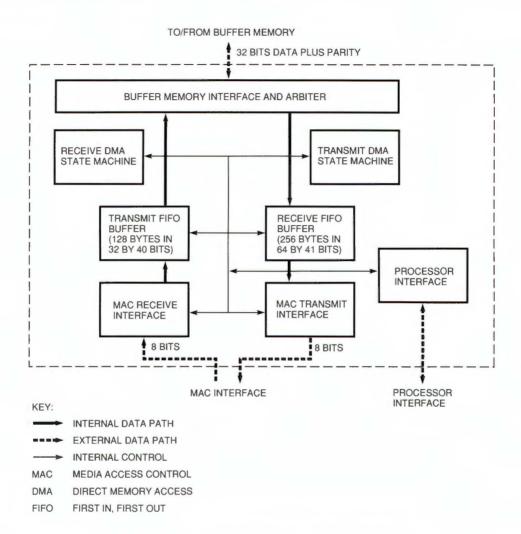

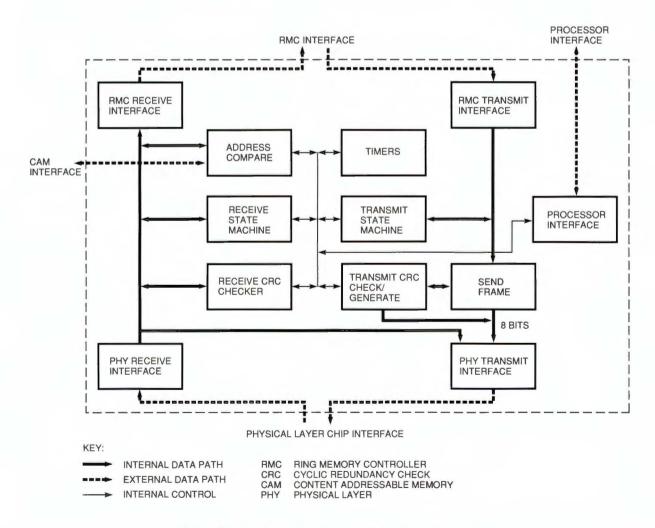

The development of physical layer hardware, used in all FDDI products, included the physical protocol (encoding/decoding) device, a receive clock recovery device, a local clock generator, and optical transmitters and receivers. This paper focuses on development of the physical layer hardware and describes some aspects of the design in detail. We first review the operation of the physical layer and the functional partitioning of the implementation. We then present detailed discussions of the distributed clock scheme, the design of an optical link, and the methods to control the effects of bit errors in the physical layer. Some of the results of the development to improve the performance, correctness, and reliability of FDDI described here have been incorporated in the American National Standards Institute (ANSI) FDDI standards.

#### Operation of the Physical Layer

The FDDI physical layer is a collection of point-topoint links forming a "ring." The operation of the layer is described in terms of physical links, physical connections, and the functions of individual stations. The many station types allowed by the ANSI FDDI standards are constructed with a simple physical layer functional block called the PHY port.

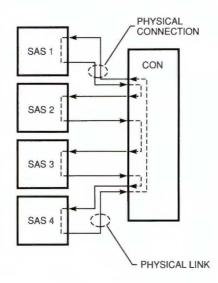

A physical link contains a transmitter, a receiver, and a segment of physical medium which conducts the bits of a packet from one station to a second station. The topology of FDDI is arranged so that the collection of physical links forms a closed path, or ring, as shown in Figure 1. This simple topology illustrates the basic concepts common to even the most complicated topologies for FDDI. Each bit of information received from one physical link is transmitted onto another physical link until the information travels around the loop and returns to where it started. The FDDI protocols provide for a single originator of data packets; other stations repeat the data so that each station on the ring receives the packet of information. The collection of many pointto-point links forms the ring, which is viewed as a multiaccess medium by the users.

The basic element in the topology of an FDDI LAN is the physical connection. A physical connection contains two physical links, also shown in Figure 1. Within the station, the circuitry that implements physical layer functionality needed for one physical connection is called the PHY port. The physical connection is a full duplex connection between

exactly two PHY ports. Neighbors in the ring directly exchange the control information for each connection, allowing control protocols in FDDI station management (SMT) to establish the shared states for a connection: in-use, starting, and disconnected. The status "in-use" indicates that a connection is part of the ring; other states indicate it is not. The control information exchanged over the physical connection is used to autoinitialize and autoconfigure the connections in the LAN, a method of operation currently unique to FDDI rings.

Figure 1 Physical Links Forming a Ring for the FDDI Physical Medium

There are several types of FDDI stations, and different types can support different numbers of physical connections. A single attachment station (SAS) (as seen in Figure 1) can establish one physical connection with a single neighbor. The dual attachment station (not shown) has two PHY ports and may establish physical connections with two neighbors. A concentrator (CON) is a type of station that can establish connections with many neighbors, thereby providing attachment points for other stations. The CON shown in Figure 1 interconnects its PHY ports internally to configure a single ring.

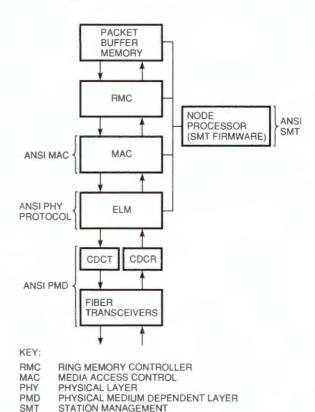

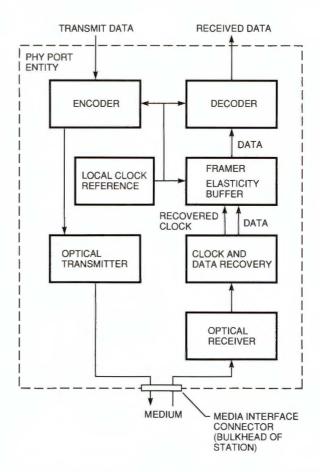

Figure 2 shows the functions of and flow of data through a PHY port which implements the FDDI physical layer protocol (PHY) standard.<sup>2</sup> Data packets to be transmitted over the LAN are passed as a stream of bytes from the data link to the physical layer. Each byte contains two PHY symbols, and each symbol represents 4 bits of user data. The FDDI coding scheme, called 4B/5B encoding, translates each

symbol into a code group containing 5 code bits. This encoding limits the maximum time between transitions on the media (allowing clock information to be derived from the coded signal) and bounds the low-frequency components of the signal spectrum. The code bits are then converted to a serial stream and transmitted as optical pulses on the fiber-optic media.

The station is coupled to the media with a media interface connector (MIC). The MIC provides the concrete interface necessary for interoperability between equipment from multiple vendors. The FDDI Physical Layer Media Dependent (PMD) standard specifies mechanical and optical properties of the MIC.<sup>3</sup> The MIC includes both a transmit and a receive interface.

Signals received from a connection are decoded by the PHY port for processing by the station. The optical input signal is translated to an electrical signal. The remote bit clock is extracted from the signal and used to recover logic levels corresponding to

Figure 2 Functional Model of the Physical Layer for an FDDI Station

the individual bits. A framer then establishes the original code group boundaries and converts the serial code bit stream into parallel form. Also, the elasticity buffer synchronizes the received data to the local clock reference and accounts for the frequency difference between the local and remote clock references. Finally, code groups of 5 code bits are decoded into symbols, and symbols are correctly paired to form the data bytes which represent the received data. These data bytes are passed either to another PHY port or to the data link layer. A later section, Operation of the Distributed Clock Scheme, expands on the elasticity buffer design.

We have so far described the FDDI physical layer in terms of PHY ports and the physical connections between them. These basic elements form the physical layer for all types of FDDI stations. Different types of FDDI stations have one or many PHY ports, but the operation of an individual PHY port and physical connection is independent of station type and topology. In the next section, we discuss the functional partitioning of the PHY port and the reasons behind the partitioning chosen. Subsequent sections describe the distributed clock scheme, the design of the physical link, and the impact of physical link errors on the LAN.

#### **Functional Partitioning**

In this section, we describe the partitioning of the functions of the PHY port into the following components:

- PHY (physical protocol chip also referred to as the ELM chip)

- CDCT (clock and data conversion transmitter)

- CDCR (clock and data conversion receiver)

- FOT (fiber-optic transmitter)

- FOR (fiber-optic receiver)

Our choices for the appropriate partitioning and technology were founded on our decision to develop a highly integrated and low-cost chip set. After examining several alternatives, we chose a partitioning that enabled us to use mostly CMOS technology (complementary metal oxide semiconductor), a minimal amount of custom ECL (emitter coupled logic), and no ECL gate array technology. Although a 125-megahertz (MHz) serial channel requires ECL circuitry in the system, we wanted to minimize the amount of custom ECL technology. ECL consumes a substantial amount of current

and is relatively expensive as compared to CMOS technology. We also considered ECL gate array technology, but decided against it because it was not a mature technology, lacked requisite analog functions for clock extraction, and was available from only a few vendors.

We determined that the CDCR and CDCT were the only functions that had to be implemented in ECL technology. This determination was based on the need for the high transmission rates and for quick conversion to and from serial and parallel data streams. The CDCR receives a 125-megabaud ECL serial data stream from the FOR. Using a phase lock loop, CDCR extracts a receive clock to recover the data bits and then converts the serial data to a 5-bit parallel bus. The CDCT receives a 25-MHz, 5-bit-wide parallel bus; then, by using a phase lock loop, it generates an internal 125-MHz transmit clock in phase with the local 25-MHz clock. CDCT then converts the 5-bit-wide parallel bus to a 125megabaud ECL serial bit stream that is transmitted by the FOT.

We selected the 5-bit width for the parallel bus to obtain a 25-MHz bus rate. This rate is a convenient divisor of the 125-MHz serial rate and is within the operating range of the CMOS gate array technology used in the connected chips. The 5-bit bus also offered the advantage of enabling us to maintain a low pin count on the devices to which the bus is interfaced, thus further containing costs.

Another complication relative to the clock component was how to distribute a 125-MHz clock signal. As noted earlier, some FDDI products have many PHY ports, and those PHY ports must have a common clock line for the transmission of the serial data stream. We decided to add another phase lock loop in the transmit component that would lock onto the 25-MHz local clock, generate the 125-MHz serial clock, and convert the 5-bit parallel bus to the serial stream. With this method, the highest clock rate distributed on our boards was a 25-MHz clock.

As a consequence of selecting the transmit phase lock loop, we chose to specify and build separate transmit (CDCT) and receive (CDCR) devices in custom ECL technology. We were very concerned that the combination of two asynchronous phase lock loops on a single chip would induce cross talk. Cross talk could cause false locking of the phase lock loops to one another, resulting in lost data. Therefore making a single chip was considered too risky for the initial implementation. Our solution was to specify the transmit and receive devices, thus eliminating the possibility of cross talk.

The balance of the logic for the physical layer protocols could now be designed in CMOS gate array technology. The use of CMOS gate arrays was important in meeting schedule since it allowed us to quickly implement changes. Changes were inevitable and therefore had to be accommodated because the ANSI standard was not finished and stable during our design cycle.

All of the physical layer functions such as the encoder, decoder, elasticity buffer, framer, and smoother were implemented in CMOS gate arrays. We had simulated these functions in software; however, we were now able to build them using CMOS gate arrays and actually analyze their behavior in real networks. With the hardware, we quickly verified the protocols defined in the FDDI standards. Proper PHY operation is best confirmed by testing actual implementations.

The fiber-optic transmitter (FOT) converts a 125-megabaud electrical signal to light pulses to be transmitted to a receiving station. The fiber-optic receiver (FOR) receives the pulses from a transmitting station and converts them to an electrical data stream. We decided not to develop the FOT and the FOR components ourselves. Instead we chose to influence the specification of the system's functional requirements in the ANSI FDDI Committee and then depend on external vendors to develop the components.

It was important to encourage the optical vendors to standardize their components so costs would decrease, and so that more than one source of optical components would be available to us. Accordingly we did not combine the optical transmitter and receiver with any other physical layer functions. The optical link design is the subject of a later section in this paper.

#### Operation of the Distributed Clock Scheme

In the FDDI distributed clocking scheme, each station uses an independent, local clock reference when transmitting or repeating data packets. The station must synchronize the receive data with its own reference clock prior to further processing. Although this distributed clock reference scheme simplifies many problems, it also can give rise to data integrity problems and packet loss rate issues that must be solved for the scheme to work effectively.

Data must be synchronized to the local clock reference in a way that prevents detected and undetected errors caused by metastability problems. Further, interpacket gap shrinkage that can result in an unacceptable packet loss rate must be controlled. In the sections Elasticity Buffer and Smoother below, we describe how these problems are addressed in the physical layer protocol.

### Elasticity Buffer

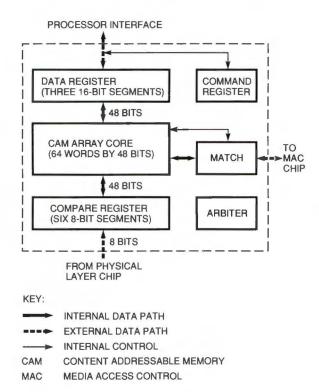

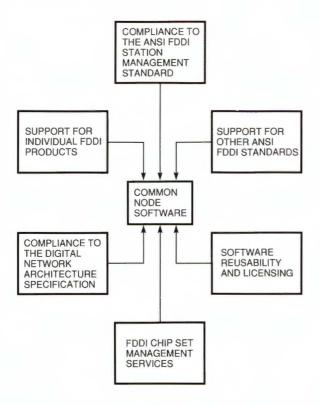

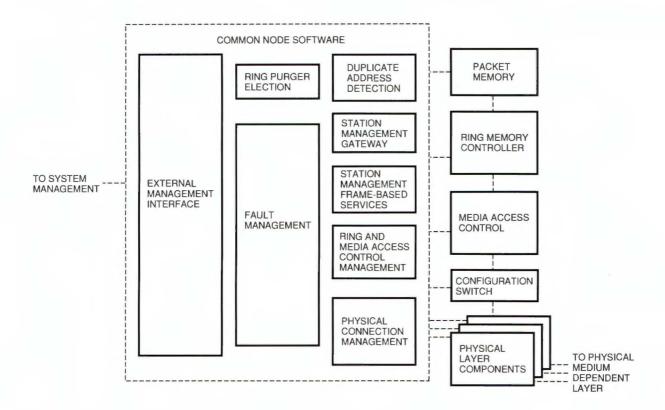

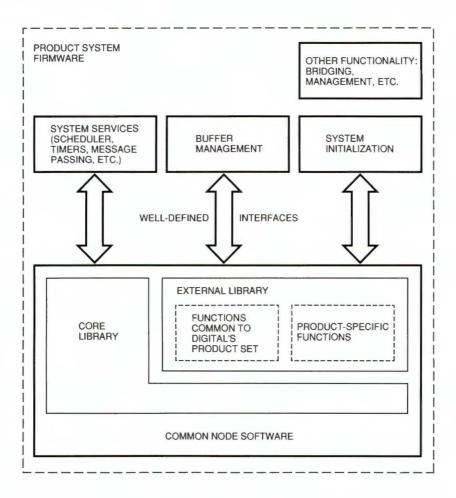

Each PHY port of a station must accept data packets from another station with a slightly different clock frequency and bit transmission rate. It is the function of the elasticity buffer within the PHY port to synchronize the incoming data to the local clock reference. The buffer is also designed to control synchronizer metastability, a source of undetected data corruption. As a result of the elasticity buffer operation, the size of the gap between two data packets varies as the packets are repeated around the ring.